#### Universidad de Cantabria

#### Departamento de Electrónica y Computadores

Tesis Doctoral

## SOPORTE ARQUITECTÓNICO A LA SINCRONIZACIÓN IMPARCIAL DE LECTORES Y ESCRITORES EN COMPUTADORES PARALELOS

Enrique Vallejo Gutiérrez Santander, Marzo de 2010

**Universidad de Cantabria**

Departamento de Electrónica y Computadores

Dr. Ramón Beivide Palacio

Catedrático de Universidad

Υ

Dr. Fernando Vallejo Alonso

Profesor Titular de Universidad

Como directores de la Tesis Doctoral:

ARCHITECTURAL SUPPORT FOR PARALLEL COMPUTERS WITH FAIR READER/WRITER

**SYNCHRONIZATION**

realizada por el doctorando Don Enrique Vallejo Gutiérrez, Ingeniero de Telecomunicación, en

el Departamento de Electrónica y Computadores de la Universidad de Cantabria, autorizan la

presentación de la citada Tesis Doctoral dado que reúne las condiciones necesarias para su

defensa.

Santander, Marzo de 2010

Fdo: Ramón Beivide Palacio

Fdo. Fernando Vallejo Alonso

Son tantas las personas a las que tengo que agradecer su ayuda y apoyo que esta sección debiera ser la más larga de la tesis. Por ello, no pretendo convertirla en una lista exhaustiva, que además, siempre se olvidaría de alguien importante. Ahí van, por tanto, mis agradecimientos condensados.

A Mónica, por su apoyo incondicional, culpable última de que tengas esta tesis en tus manos.

A mi familia, especialmente a mis padres, por el soporte y apoyo recibido.

A mis directores de tesis, Mon y Fernando. Aunque esto sea una carrera en solitario, es necesaria una buena guía para llegar al final.

A los revisores de la tesis, tanto los revisores externos oficiales, Rubén González y Tim Harris, como todos aquellos que se molestaron en leer el trabajo y ayudaron con sugerencias y posibles mejoras.

A los compañeros del Grupo de Arquitectura y Tecnología de Computadores de la Universidad de Cantabria, por la ayuda y colaboración en el desarrollo del trabajo, en especial a Carmen Martínez.

A la gente del BSC-MSR Center y de la UPC, en especial a Mateo Valero y Adrián Cristal. Sin su trabajo previo en Kilo-Instruction Processors esta tesis hubiera sido imposible; pero también lo hubiera sido sin su guía, ayuda y apoyo y dirección durante su desarrollo. També voldria agrair l'ajuda i col·laboració dels companys del Departament d'Arquitectura de Computadors de la UPC, especialment a Miquel Moretó, i del BSC. You all know who you are, locos.

I meet a lot of bright and helpful people during my internship in the Systems and Networking Group in Microsoft Research Cambridge, and they all deserve a sincere acknowledgement. But specially, I had the luck to work under the supervision of Tim Harris. He deserves a double acknowledgement. First, for his help, support and encouraging during my internship and the subsequent work. Second, because most of the work presented here would have been impossible without his prior pioneering work on nonblocking synchronization and Transactional Memory. Thanks, Tim.

A todos mis amigos que tuvieron que sufrir de vez en cuando alguna aburrida explicación (culpa suya, por preguntar...) y supieron recordarme que de vez en cuando que existe un mundo real al otro lado de la pantalla.

This work has been partially supported by the Spanish Ministry of Education and Science / Ministry of Science and Innovation, under contracts TIN2004-07440-C02-01, TIN2007-68023-C02-01, CONSOLIDER Project CSD2007-00050 and grant AP-2004-6907, by Microsoft Research Cambridge and by the joint BSC-Microsoft Research Centre. The author would also like to thank the support of the European Network of Excellence on High-Performance Embedded Architecture and Compilation (HiPEAC).

#### Resumen

La evolución tecnológica en el campo de los microprocesadores nos ha llevado a sistemas paralelos con múltiples hilos de ejecución simultánea, o *threads*. Estos sistemas son más difíciles de programar y presentan sobrecargas en la ejecución mayores que los sistemas uniprocesadores tradicionales, lo que puede limitar su rendimiento y escalabilidad. Estas sobrecargas se deben principalmente a los mecanismos de sincronización, el protocolo de coherencia y el modelo de consistencia y otros detalles requeridos para garantizar una ejecución correcta.

El Capítulo 1 de esta tesis hace una introducción a los mecanismos necesarios para diseñar y hacer funcionar tal sistema paralelo, detallando en gran medida el trabajo reciente del área. En primer lugar, el apartado 1.1 estudia los mecanismos que hacen posible la construcción de sistemas de memoria común: El protocolo de coherencia y el modelo de consistencia del sistema. Estos dos mecanismos garantizan que los diferentes procesadores tienen una visión uniforme de la memoria del sistema, y especifican cómo puede comportarse el sistema cuando hay carreras en el acceso a datos compartidos. A continuación, en el apartado 1.2 se exponen los fundamentos de la programación paralela en tal modelo de memoria común, con énfasis en los mecanismos de sincronización: barreras y secciones críticas protegidas por locks. Se discuten las principales dificultades que presenta esta programación paralela con respecto a la programación single-threaded: la ley de Ahmdal, que limita la escalabilidad del sistema por la componente secuencial de los programas; el compromiso en cuanto al nivel de granularidad del paralelismo, en que una granularidad más fina permite más paralelismo pero presenta más overhead en la ejecución; los problemas de deadlock (interbloqueo), inversión de prioridad y starvation (inanición), inherentes a sistemas basados en locks; y finalmente, se analiza la complejidad del diseño de estructuras de datos concurrentes, especialmente por dos problemas: la dificultad de ampliar una estructura de datos con nuevos métodos sin conocer en detalle la implementación del resto de métodos, y la falta de composibilidad, es decir, que la construcción de una estructura de datos de un nivel superior, a partir de estructuras basadas en locks más sencillas, puede dar lugar a deadlock.

Existen múltiples implementaciones alternativas de *locks*, que se revisan en el apartado 1.3. En esencia, un *lock* es una abstracción que protege una cierta zona de memoria o parte del

código, de forma que sólo un thread pueda acceder a la zona protegida. Alternativamente, existen locks de lectura/escritura, que permiten un único escritor que modifique los datos, o múltiples lectores que accedan a la vez a los datos compartidos sin modificarlos. Hay implementaciones centralizadas, en que el lock es una única palabra de memoria a la que se accede mediante operaciones atómicas del procesador. Una implementación así genera contienda: todos los threads que quieren tomar el lock acceden a la misma posición de memoria, lo que implica múltiples invalidaciones a nivel de coherencia, empeorando el rendimiento del sistema. Alternativamente, existen implementaciones distribuidas, como los locks basados en colas: cada thread que quiera tomar el lock reserva una estructura denominada "nodo" en memoria, y los diferentes nodos de cada thread se enlazan en forma de una cola de solicitantes. En estos diseños el lock se pasa en orden de un nodo al siguiente, lo que evita la contienda, y además garantiza el fairness: existe una política que garantiza que todos los threads que pretenden tomar un lock lo consiguen hacer en un tiempo razonable, sin producirse starvation. En este apartado 1.3 se discuten también múltiples alternativas de locks, como aquellos que abortan si el lock no se toma en un cierto periodo de tiempo (trylocks), las implementaciones jerárquicas, o locks diseñados para comportarse especialmente bien en caso de existir un comportamiento patológico, como ser adquirido siempre por el mismo thread (biased locks).

Una propuesta relativamente reciente que aborda los problemas de programación paralela es la Memoria Transaccional (*Transactional Memory*, TM), que se introduce en el apartado 1.4. Un sistema de Memoria Transaccional proporciona al programador la abstracción de una transacción con la que puede realizar modificaciones en memoria compartida. Las transacciones en memoria son análogas a las transacciones de las bases de datos, garantizando las propiedades de atomicidad (se ejecuta toda la transacción, o se aborta toda la transacción, pero no parte de ella) y aislamiento (ningún *thread* es capaz de ver el estado intermedio de otra transacción) al código que corre dentro de la transacción. Esto permite eliminar la gestión de *locks* de la tarea de programación al sustituir secciones críticas por transacciones, evitar el problema de *deadlock*, simplificar la modificación de código existente y proporcionar *composibilidad*.

Para garantizar una ejecución correcta, el sistema de Memoria Transaccional debe ejecutar el código transaccional de manera especulativa, almacenando los cambios que realiza la transacción (el write-set) en algún tipo de buffer, y utilizar un mecanismo de validación (commit) que garantice que los cambios se hacen visibles a nivel global (al resto de threads) de forma atómica, sin que hayan ocurrido cambios en las posiciones de memoria leídas (el readset). Además, el sistema debe detectar las violaciones: si dos transacciones acceden de manera concurrente a los mismos datos en memoria (solapándose parcialmente el write-set de una de ellas con el read-set o el write-set de la otra) una de las transacciones debe pararse y esperar al commit de la otra, o abortar y reiniciarse. El mecanismo que decide la acción cuando se detecta un conflicto se denomina contention manager.

Existen múltiples implementaciones de Memoria Transaccional, tanto en software (STM), como propuestas Hardware (HTM) o propuestas tanto híbridas como aceleradas por *hardware* (HyTM o HaTM), que ejecutan parte de las operaciones (como el versionado de los datos) en software, y otra parte (como la detección de conflictos) mediante hardware específico. Los sistemas hardware proporcionan un rendimiento mucho mayor, al eliminar ciertas tareas que pueden requerir un tiempo de ejecución lineal con el tamaño del *read/write-set*. Sin embargo, en el momento de escribir este texto, no existe todavía ninguna implementación comercial de sistemas HTM; El procesador Rock de Sun [22] pretendía soportar un sistema híbrido, pero su producción ha sido cancelada.

En el apartado 1.4 se discuten múltiples detalles que condicionan o limitan una implementación de Memoria Transaccional. Uno de estos detalles es el problema de la privatización: Los datos compartidos pueden disponer de alguna variable que permita hacerlos privados y acceder a ellos sin necesidad de utilizar transacciones. Sin embargo, en múltiples implementaciones de STM pueden darse carreras de datos que hacen que los datos se modifiquen simultáneamente desde una transacción y desde el código externo, sin que se advierta la colisión. En el apartado 1.4.6 se discuten el problema y diferentes soluciones. Otro detalle es la política utilizada en el *contention manager*. En general, en sistemas HTM el *contention manager* es muy simple, utilizando una política sencilla que elige una transacción u otra en función de algún parámetro, como pueda ser el uso de un *timestamp*. Otra dificultad puede ser la ejecución de operaciones irrevocables, es decir, aquellas que no pueden deshacerse en caso de tener que abortar la transacción. Ejemplos de estas operaciones son la entrada/salida o las operaciones del sistema que operan sobre procesos. Para gestionarlo, el sistema debe soportar las transacciones irrevocables, es decir, transacciones que se garantiza que van a finalizar sin abortar, y que el *contention manager* siempre elige con preferencia.

Aunque la Memoria Transaccional libera al programador de la complejidad de la gestión de *locks*, muchos de los sistemas STM actuales están internamente basados en *locks* de escritura [36, 46, 124]. Una implementación así, aunque puede bloquearse puntualmente (cuando un *thread* que ha tomado un *lock* es sacado temporalmente de ejecución), es más sencilla y flexible que una implementación no bloqueante [42]. Además, Dice y Shavit discuten [34] las ventajas de utilizar una implementación basada en *locks* de lectura/escritura, básicamente: es inmune al problema de la privatización; presenta una implementación interna sencilla, sin costosos procesos de validación; mejor *fairness* al implementar lectores visibles, especialmente en transacciones largas; y soporte sencillo para operaciones irrevocables. Sin embargo, el rendimiento de un sistema así está limitado por el alto coste de tomar *locks* de lectura en todas las posiciones de memoria leídas en la transacción.

Finalmente, el apartado 1.5 se centra en la evolución del diseño de los microprocesadores. La tecnología actual permite niveles de integración que no merece la pena explotar con un único hilo de ejecución, ya que las mejoras de la arquitectura según aumenta el número de

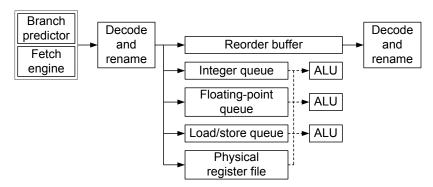

transistores proporcionan beneficios marginales. El principal problema es que las implementaciones actuales incorporan múltiples elementos que no se pueden escalar sin afectar al tiempo de ciclo, como las memorias direccionables por contenido (*Content-Adressable Memory*, CAM) utilizadas en las colas de Load-Store (*Load-Store Queue*, LSQ) o el buffer de reorden (*Reorder Buffer*, RoB), o el tamaño del banco de registros. Esto hace que no pueda aumentarse el tamaño de la ventana de instrucciones (número de instrucciones en vuelo en el procesador) de forma acorde con el aumento del tiempo de acceso a memoria.

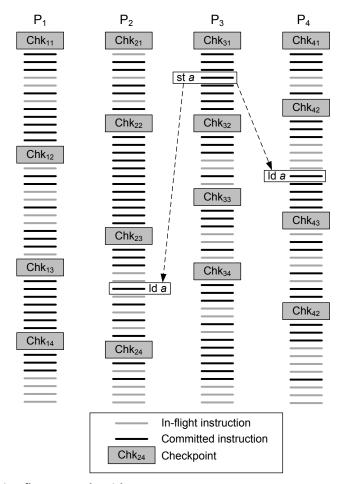

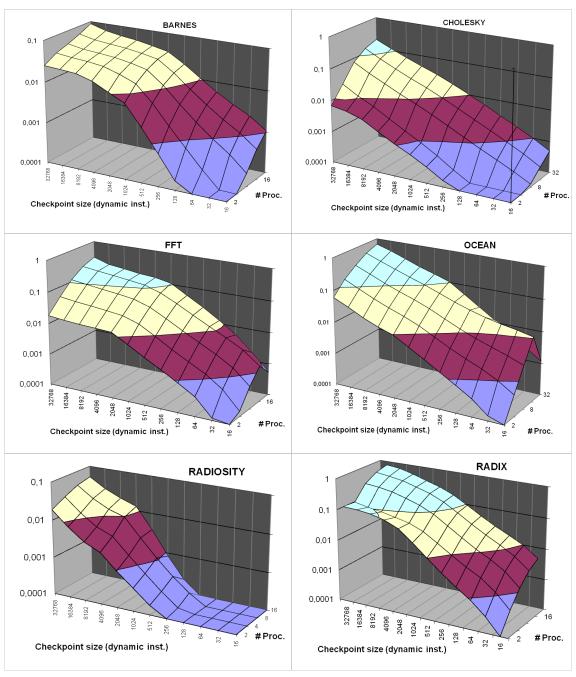

En este apartado 1.5 se citan un conjunto de técnicas recientes que pretenden proporcionar una arquitectura con un tamaño de ventana de instrucciones muy grande, del orden del millar de instrucciones, para atacar el aumento en el tiempo de acceso a memoria principal. Conjuntamente, una arquitectura con estas técnicas se ha denominado *Kilo-Instruction Processor* [30]. Específicamente, se proponen arquitecturas basadas en *checkpoints* que eliminan el RoB y realizan la validación de todas las instrucciones correspondientes al mismo *checkpoint* conjuntamente; Mecanismos de reducción del número de registros físicos necesarios para un cierto tamaño de ventana; implementaciones jerárquicas de la LSQ, acordes con la arquitectura de *checkpoints*; y otras técnicas que permiten la escalabilidad de los recursos del procesador y su ventana de instrucción para que soporte latencias más grandes. Conjuntamente, estas técnicas permiten explotar el paralelismo a nivel de instrucción en el procesador, a pesar de la existencia de grandes latencias en la memoria principal.

Todos los aspectos citados condicionan el rendimiento y el diseño de un sistema paralelo de memoria común. El objetivo de esta tesis es introducir una serie de técnicas, principalmente en *hardware*, para acelerar la ejecución de estos programas paralelos.

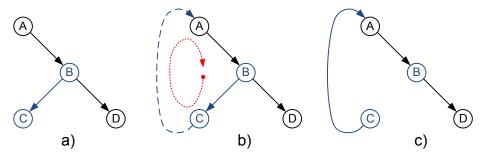

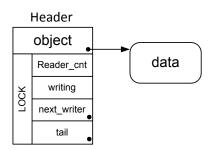

El Capítulo 2 introduce un sistema de Memoria Transaccional híbrido basado en *locks* de lectura/escritura. Se ha comentado las ventajas de un sistema basado en estos *locks*, así como el problema de rendimiento que presentan en un STM. Para abordar este aspecto, se propone una modificación al *runtime* de un STM tal que, en caso de disponer de un sistema HTM genérico, la mayoría de la ejecución se aproveche de sus capacidades. El STM base utiliza la versión de lectura/escritura del *lock* MCS [107]. En general, se mantiene un *lock* por cada objeto transaccional y se permite la ejecución de transacciones *software* o *hardware* concurrentemente. Para ello, se añaden los siguientes cambios:

- Si el soporte hardware está presente, se comienza una transacción hardware junto con la transacción software.

- En cada acceso a un objeto desde una transacción hardware, se verifica el estado del lock, para detectar conflictos con transacciones que se ejecuten en software, y por tanto que tomen los locks en el modo correspondiente. Para ello, la cabecera del lock se modifica de forma que la transacción hardware pueda detectar conflictos con lectores o escritores sin necesidad de seguir la cola de punteros del lock. Si se detecta

un conflicto con una transacción *software*, la transacción *hardware* aborta, ya que no puede esperar a que la otra llegue al *commit*.

En cada acceso a un objeto transaccional, el versionado y la detección de conflictos se pueden delegar al HTM. En el apartado 2.3 se discuten diferentes alternativas que descargan diferente cantidad del trabajo en el HTM, y proporcionan diferente rendimiento, junto con las implicaciones sobre los campos a modificar de las cabeceras.

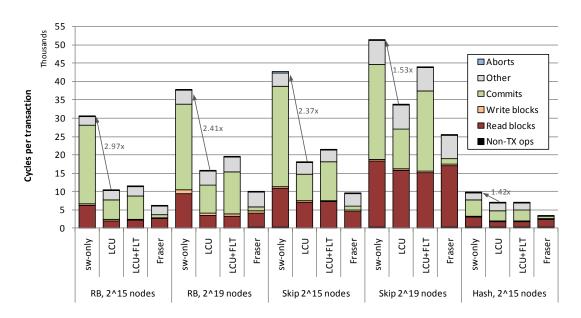

El sistema presentado se evalúa con el simulador GEMS [101] y mediante diferentes microbenchmarks transaccionales. Los resultados muestran que la aceleración hardware mejora el rendimiento por varios motivos. En primer lugar, la cantidad de trabajo del runtime que no se ejecuta gracias al soporte hardware proporciona un speedup entre 1.68× y 3.45× en el mejor de los modos. Además, el soporte hardware evita la congestión de lectura en la raíz de ciertas estructuras de datos como árboles o listas. Específicamente, la raíz de estas estructuras es leída en todas las transacciones, lo que genera una importante contienda a nivel de coherencia en el acceso al lock correspondiente en modo lectura. En cambio, con el soporte hardware estos accesos se reducen a una simple comprobación, que no genera invalidaciones de coherencia. Esto hace que la escalabilidad del sistema sea mucho mayor con el soporte hardware que en el STM base. Finalmente, se estudia el número de reintentos en modo hardware antes de revertir al modo más lento y seguro, en software. Los resultados indican que, a falta de algún tipo de indicación por parte del hardware (por ejemplo, del motivo por el que aborta una transacción), el número óptimo de reintentos crece con el número de threads en el sistema. Los resultados también muestran, sin embargo, que el rendimiento del sistema hardware sufre cuando el nivel de congestión es grande. Este problema tiene una doble raíz: Por una parte, al aumentar el número de transacciones hardware que abortan y pasan al modo software, la ejecución es más lenta. Por otra parte, la ejecución concurrente de transacciones hardware y software, con diferentes políticas de control de congestión, puede introducir starvation, lo que penaliza el rendimiento. Este aspecto se estudia en el apartado siguiente.

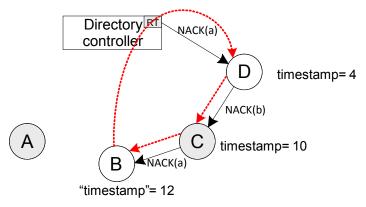

El Capítulo 3 estudia los problemas de *starvation* causados por falta de *fairness* en el acceso a los datos entre transacciones *hardware* y *software*. En concreto, las transacciones software requieren tomar un lock en cada objeto accedido en el momento de hacer el *commit*. Las transacciones *hardware*, en cambio, solo requieren comprobar el estado de dicho *lock* en el momento de acceder al objeto. El aislamiento del sistema HTM garantiza que los accesos realizados (por ejemplo el acceso al *lock*) se mantienen inalterados hasta el final de la transacción. Esto se traduce en que cualquier intento por parte de otro *thread* de modificar la variable leída (por ejemplo, una transacción software que pretenda tomar el *lock*) se verá retrasado hasta después del *commit* de la transacción *hardware*. En concreto, con el modelo HTM utilizado, LogTM [110], el aislamiento se garantiza en base a una extensión del protocolo

de coherencia que envía confirmaciones negativas (NACK) para evitar accesos que entrarían en conflicto con una transacción existente.

Claramente, el sistema HyTM propuesto favorece a las transacciones *hardware*. Esto, de por sí, no es problemático, ya que éstas son el caso más frecuente y el más rápido. Sin embargo, el sistema puede generar *starvation* en las transacciones *software* si un objeto es leído frecuentemente por transacciones *hardware* y pretende ser modificado por una transacción software. En este caso, la transacción *software* debería esperar a que no hubiera ninguna transacción *hardware* accediendo al objeto; sin embargo, como múltiples transacciones *hardware* pueden leer el objeto en paralelo (diferentes lecturas a nivel de coherencia no constituyen una violación), puede darse el caso en que siempre haya alguna transacción *hardware* accediendo en modo lectura a un objeto. Esto puede parar indefinidamente a una transacción *software* que pretenda escribirlo, generando *starvation*. Este problema ocurre frecuentemente en nuestros benchmarks en el caso de estructuras de datos con un único punto de entrada, como una lista o un árbol binario.

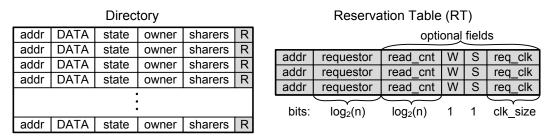

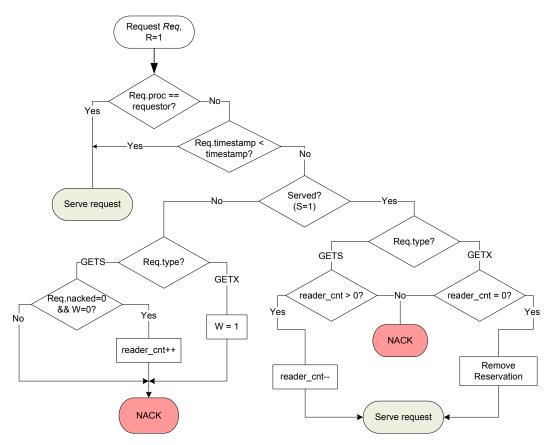

Para abordar este problema, en el apartado 3.2 se propone un mecanismo *hardware* para reservar ciertas líneas en el directorio, basado en una estructura denominada *Reservation Table* (RT). La RT es una pequeña tabla, con unas 4 entradas, colocada junto al controlador de memoria. Cuando un procesador recibe un NACK a una petición de coherencia, envía una petición de reserva a la RT. A partir de ese punto, se registra ese bloque concreto como reservado para un cierto procesador, y no se atiende (a nivel de coherencia) a ninguna petición de otro procesador. Además, se proporciona un mecanismo de notificación, que garantiza que las transacciones HTM, una vez finalizada su ejecución, liberan el bloque de sus caches, evitando accesos consecutivos. Finalmente, se estudia el problema del *deadlock* en este sistema, mostrando cómo la implementación más sencilla de la RT puede generarlo, y se proporciona una política que es compatible con el sistema de *timestamps* del HTM base, LogTM.

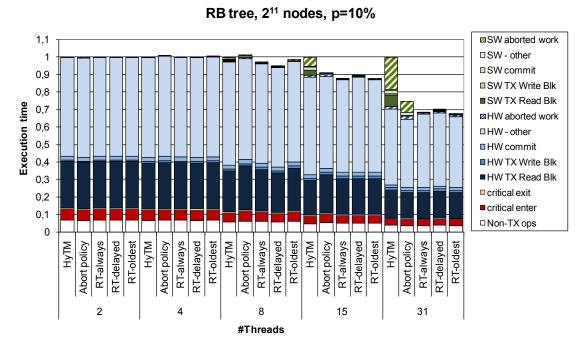

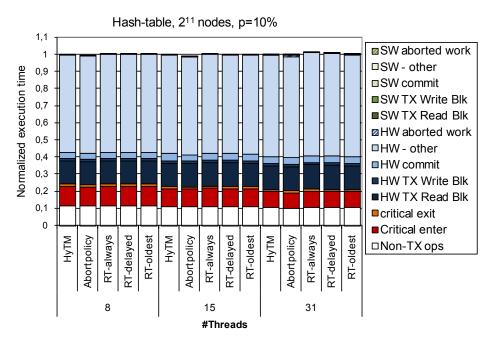

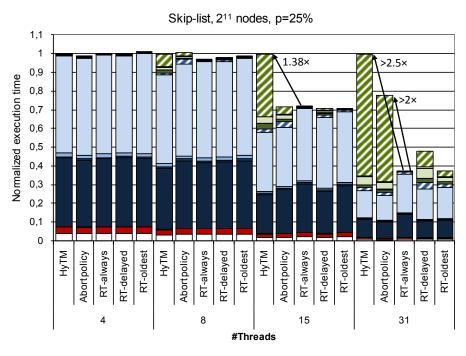

El sistema propuesto se ha implementado en la misma infraestructura de simulación indicada antes. Las evaluaciones muestran un *speedup* considerable en aquellas aplicaciones con mucha congestión, mientras que el rendimiento en los casos no congestionados no sufre. Especialmente, se compara el rendimiento obtenido con nuestro mecanismo, frente a una política que pretende abordar el mismo problema en sistemas HTM propuesta en [16]. En el caso de la política para sistemas HTM, la solución es abortar las transacciones hardware que generan el *starvation*. En el caso de nuestro sistema híbrido, esto aumenta el número de transacciones abortadas, y la proporción de transacciones que se ejecutan en software, reduciendo el rendimiento. Por el contrario, la RT minimiza el número de abortos y por tanto el paso al modo software, lo que proporciona *speedups* de hasta 2× en casos congestionados.

Vista la importancia de los *locks* de lectura/escritura, el Capítulo 4 se centra en mecanismos *hardware* de aceleración de estas operaciones de sincronización, para reducir los *overheads*

asociados. En concreto, existen diferentes propuestas para la implementación en hardware de operaciones de sincronización, que se citan en el apartado 4.1. Diferentes implementaciones asocian un cierto estado a cada palabra de memoria [6, 8, 32, 76, 80], construyen colas hardware de solicitantes para conseguir una transferencia del *lock* rápida [55], o asignan *locks* de lectura/escritura dinámicamente a cualquier posición de memoria arbitraria [159]. Sin embargo, todas estas propuestas tienen diferentes limitaciones que, a nuestro entender, pueden restringir su utilización a un punto de vista puramente académico o de investigación. En concreto, algunas de las limitaciones que encontramos en las propuestas existentes, que se resumen en la Tabla 4-1, son:

- En múltiples propuestas resulta necesario añadir tags a todas las líneas de memoria o palabras del sistema, lo que aumenta considerablemente los recursos utilizados.

- La mayoría de las propuestas no permiten utilizar *locks* de lectura/escritura.

- La escalabilidad está restringida en múltiples propuestas a un sistema basado en un bus central con *snoopy*, o a un único CMP.

- En la mayoría de los casos el sistema es inflexible; por ejemplo, por requerir una asociación estática de *threads* a procesadores, y fallando en el caso de migración de un procesador a otro; por fallar en el caso de realizarse operaciones migración de páginas en aquellas con *locks* activos; por limitar el número de *locks* que se pueden tomar en un momento dado; o por no permitir el uso de trylocks que abortan si no es tomado en un intervalo dado.

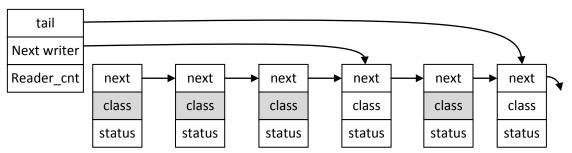

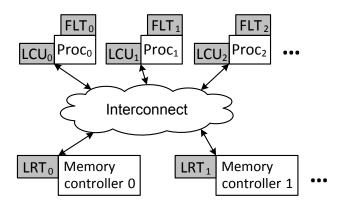

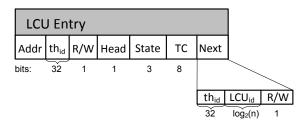

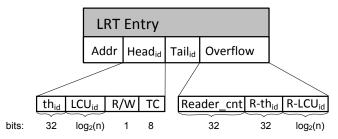

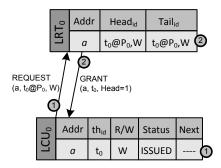

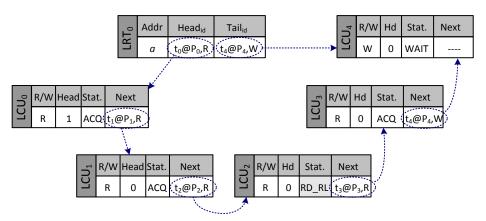

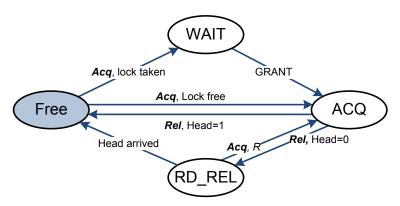

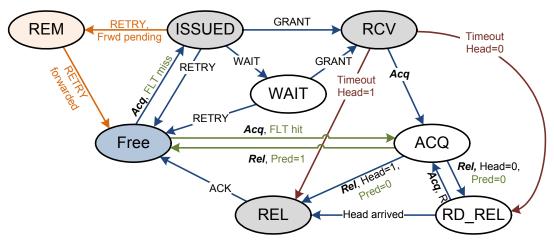

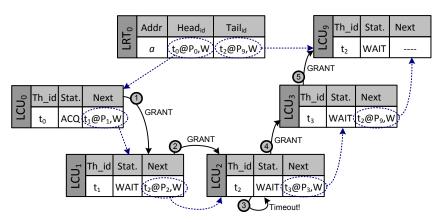

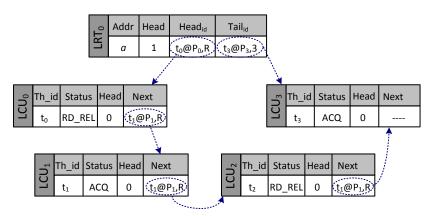

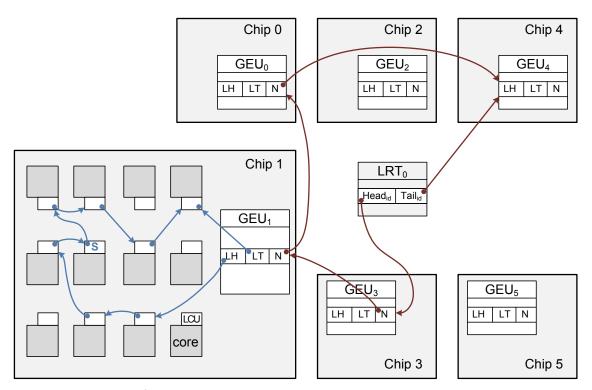

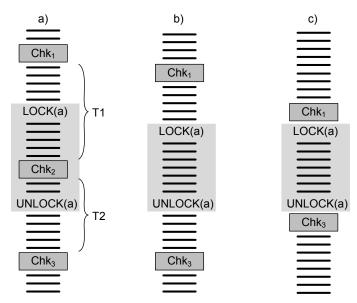

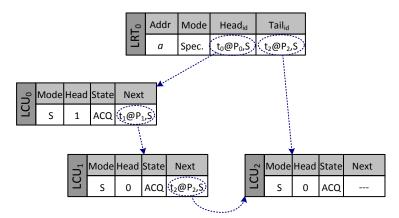

En el apartado 4.2 se introduce el mecanismo del *Lock Control Unit* (LCU). Este sistema busca proporcionar un sistema *hardware* flexible y escalable para gestionar *locks*, con un *overhead* pequeño y un tiempo de transferencia del *lock* bajo. En concreto, nuestra propuesta utiliza una unidad hardware, la *Lock Control Unit* (que a su vez da nombre a todo el sistema) asociada a cada procesador. La LCU recibe las peticiones del procesador, y está compuesta de una tabla con múltiples entradas, utilizándose una por cada *lock* a gestionar, así como la lógica de control necesaria. El procesador utiliza nuevas instrucciones para tomar y liberar un *lock* en cualquier posición de memoria arbitraria, en modo lectura o escritura. Las entradas de la LCU se utilizan como interfaz con el procesador, que itera en la consulta de la entrada local correspondiente hasta que el *lock* se obtiene, y como nodos de una cola de solicitantes.

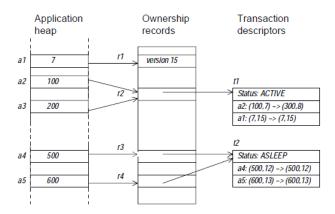

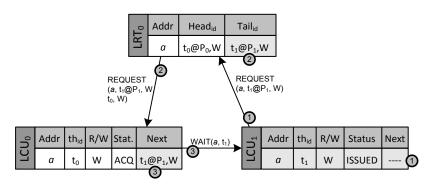

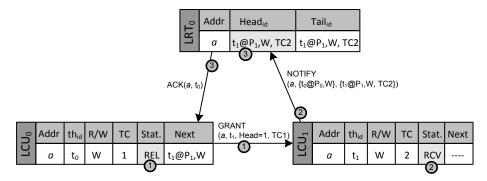

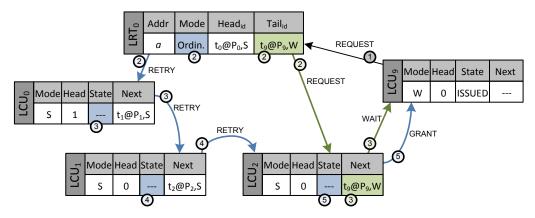

A nivel global, existe una o varias estructuras denominadas *Lock Reservation Table* (LRT). Esta estructura es la que se encarga de orquestar el acceso a un mismo *lock* por parte de diferentes LCUs. Cada *lock* se asocia a una LRT de forma unívoca según su dirección física, lo que permite disponer de múltiples LRTs, por ejemplo una por cada controlador de memoria. Cuando una LCU recibe una petición para un *lock* en una nueva posición de memoria, envía una solicitud a la LRT correspondiente, en función de la dirección física del *lock*. Si el *lock* no existía

previamente, la LRT asigna una nueva entrada en su tabla, y concede el *lock* a la LCU solicitante. En cambio, si el *lock* ya existía con una entrada en la LRT correspondiente, se reenvía la solicitud al último LCU solicitante. Éste guarda un puntero del nuevo solicitante, generándose así una cola enlazada que se utilizará para la transferencia directa del *lock* entre las diferentes LCUs. Cuando una LCU recibe la concesión del *lock*, el procesador local, que se encuentra iterando sin éxito intentando adquirirlo, lo consigue al fin y accede a la sección crítica. La transferencia del *lock* de una LCU a otra implica una notificación a la LRT correspondiente, para garantizar que se mantienen correctos los punteros de cabeza y final de la cola. Sin embargo, estas notificaciones están fuera del camino crítico de la transferencia del *lock*, lo que evita interferencias en el traspaso del mismo.

El sistema de la LCU permite tomar los *locks* en dos modos. En primer lugar, está el modo ordinario, basado en la construcción de una cola, que se ha indicado antes. Además, existe un modo denominado *overflowed locking*, que permite eliminar la entrada de la LCU. Cuando no hay más solicitantes para un *lock*, se puede eliminar la entrada de manera segura, ya que los metadatos correspondientes están registrados en la LRT por si fuera necesario comenzar una cola al recibir nuevas peticiones. De esta forma, en un sistema que utilice *fine-grain locking* un mismo procesador puede tomar múltiples *locks* sin que el número de entradas de la LCU constituya un problema, ya que pocos de estos *locks* tendrán una cola asociada.

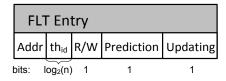

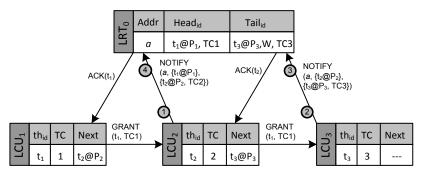

El sistema propuesto también permite el uso de *locks* de lectura/escritura. Múltiples nodos consecutivos de la cola pueden recibir la concesión de un *lock* en modo lectura, y ésta concesión no se transmite al siguiente solicitante hasta que todos los lectores han liberado su *lock*, en cualquier orden. Finalmente, se propone una estructura opcional adicional, denominada la *Free Lock Table* (FLT). En los casos en que un *lock* es tomado repetidamente por un mismo *thread*, el *lock* puede guardarse en la FLT local al ser liberado, lo que permite un acceso más rápido en la siguiente operación y evita las notificaciones externas innecesarias.

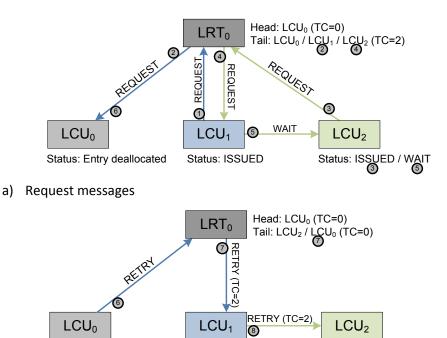

Existen propuestas hardware que asignan los locks al procesador solicitante. El sistema propuesto, por contra, asigna cada lock a un thread, no a un procesador, pero registrando el número de procesador desde el que realizó la petición para tareas de direccionamiento. Esto permite que, mediante un mecanismo de punteros apropiado, se soporten los casos en que un thread migra de un procesador a otro, tanto con el lock tomado, como cuando es parte de la cola. Especialmente, la LCU implementa un temporizador que, tras recibir un lock, lo transfiere al siguiente solicitante tras un periodo de tiempo si éste no ha sido tomado, evitando starvation temporal o deadlock en los casos de suspensión o migración del thread solicitante.

El apartado 4.2.3 incluye un estudio detallado de la implementación del mecanismo propuesto. En este apartado se proponen una serie de invariantes que debe cumplir el sistema. También se estudia cómo se evitan las carreras de datos, por ejemplo en las notificaciones a la LRT cuando se transfiere un *lock*. Se analiza la máquina de estados a implementar en cada entrada de la LCU. Se estudian los casos de *overflow* de recursos, es

decir, cómo se comporta el sistema cuando no quedan disponibles entradas en la LCU local, o en la LRT; El primer caso se resuelve mediante el uso de entradas especiales que solo pueden tomar los *locks* en el modo de *overflow*, y con políticas que garantizan que éstos *locks* queden libres para ser tomados sin necesidad de una cola; El segundo caso, se gestiona desbordando las entradas de la LRT a una estructura de datos en memoria principal. También se analiza cómo puede el mecanismo soportar los eventos de paginación o sistemas virtualizados, aunque en estos casos no se propone un mecanismo detallado al ser altamente dependiente de la implementación concreta. Finalmente, este apartado también propone dos optimizaciones del sistema base, por una parte para optimizar la patología en que un *lock* es tomado casi exclusivamente en modo de lectura (como la raíz de una estructura de datos) y por otra parte, para mejorar el rendimiento en sistemas con una estructura jerárquica, como pueda ser un sistema compuesto por múltiples CMPs.

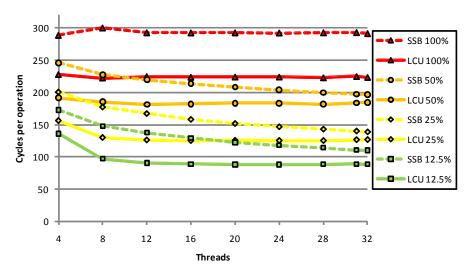

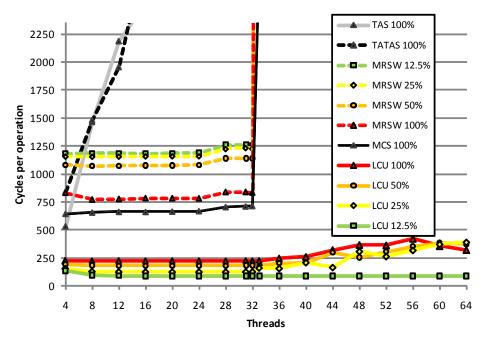

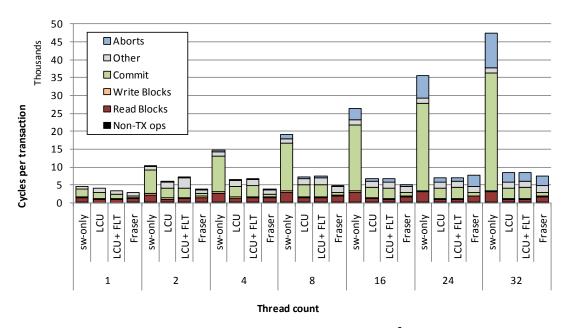

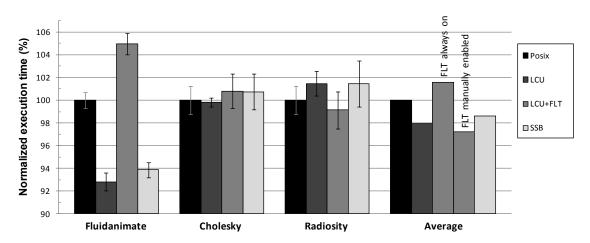

El mecanismo de la LCU ha sido evaluado en la misma plataforma de simulación, y los resultados se muestran en el apartado 4.3. En primer lugar, se estudia cómo se minimiza el número de mensajes en el camino crítico de la transferencia del lock, al requerirse una única notificación. Especialmente, este resultado mejora mucho el valor obtenible mediante locks software. Éstos dependen del protocolo de coherencia, e incluso la mejor implementación basada en colas requiere 4 ó 6 mensajes en función del protocolo, considerando las invalidaciones de coherencia involucradas. A continuación, se utiliza un microbenchmark para medir el tiempo de transferencia del lock con múltiples threads accediendo a la misma sección crítica. La latencia obtenida supera con creces cualquier lock software, y también propuestas hardware que no construyen una cola de solicitantes. El sistema STM basado en locks de lectura/escritura, utilizado como base en el Capítulo 2, se utiliza aquí como benchmark que utiliza fine-grain locking. Los resultados muestran que la LCU evita la congestión de lectura de los locks MCS originales, y que su menor overhead proporciona speedups entre 1.46× y 2.97× según la aplicación, con 16 threads. Finalmente, se utilizan aplicaciones paralelas tradicionales de las suites SPLASH-2 [157] y PARSEC [13]. Los resultados en este caso son más modestos, ya que la proporción del tiempo de ejecución destinado a tareas de sincronización es mucho menor en estos benchmarks. En promedio, el sistema consigue un speedup de 2.9% utilizando en cada caso la configuración óptima, con o sin FLT.

El Capítulo 5 pasa a considerar la microarquitectura del procesador, especialmente en lo relativo a las tareas de sincronización basadas en *locks*. Este Capítulo no evalúa ninguna propuesta mediante simulación, sino que discute las posibilidades de organización del sistema considerando una arquitectura basada en *Kilo-Instruction Processors*. En primer lugar, se introduce la idea de *transacciones implícitas* como modelo de organización de un procesador basado en *checkpoints*, como los estudiados en la Introducción. Se muestra cómo la validación atómica de un *checkpoint* a nivel global proporciona un comportamiento similar al caso de la memoria transaccional. También se estudia cómo esto permite simplificar el modelo de

consistencia (proporcionando un modelo de Consistencia Secuencial) al tiempo que se persigue un rendimiento elevado al explotarse el ILP en el resto de *checkpoints* en vuelo.

Este Capítulo también estudia diferentes posibilidades para la especulación en secciones críticas gracias a la citada capacidad transaccional. En primer lugar, se muestra cómo un mecanismo de detección y eliminación de *silent stores* temporales permite la especulación en *locks software*. Además, se argumenta cómo esa implementación es factible, gracias a la implementación jerárquica de la cola de load/stores propuesta para los *Kilo-instruction Processors*. Después, se discute la implementación del mecanismo de la LCU y su interfaz con la microarquitectura. En concreto, es necesaria una cola llamada *LCU buffer* que almacena las operaciones de sincronización de cada *checkpoint*. Además, es necesario adelantar las adquisiciones de *locks* antes del *commit* del *checkpoint* en que se ejecutan, con la consiguiente acción de compensación (la liberación del mismo *lock*) en caso de abortarse la transacción. Finalmente, se argumenta cómo el mecanismo de la LCU propuesto en el Capítulo 4 no permite la especulación en secciones críticas, y se esboza una modificación con un modo de adquisición especulativo que sí que lo permitiera.

Como resumen, esta tesis propone una serie de mecanismos hardware y software para simplificar la programación de sistemas paralelos de memoria común y aumentar su rendimiento, centradas en torno a la programación con locks de lectura/escritura con garantías de fairness. Estas propuestas se han realizado en diferentes ámbitos: diseñando un sistema híbrido de Memoria Transaccional basado en estos locks; proporcionando mecanismos que garantizan el fairness en dicho sistema entre transacciones hardware y software; proponiendo un mecanismo hardware de aceleración de los locks fair de lectura/escritura; y estudiando la relación entre estos mecanismos de sincronización y la microarquitectura del procesador, centrándose en arquitecturas basadas en checkpoints. Adicionalmente, se han abierto varias vías de investigación, principalmente en lo relativo a implementaciones hardware de locks de de lectura/escritura.

#### University of Cantabria

#### Department of Electronics and Computers

**Doctoral Thesis**

# ARCHITECTURAL SUPPORT FOR PARALLEL COMPUTERS WITH FAIR READER/WRITER SYNCHRONIZATION

Enrique Vallejo Gutiérrez Santander, March 2010

Technological evolution in microprocessor design has led to parallel systems with multiple execution threads. These systems are more difficult to program and present higher performance overheads than the traditional uniprocessor systems, what may limit their performance and scalability. These overheads are due to the synchronization, coherence, consistency and other mechanisms required to guarantee a correct execution.

Parallel systems require a deeper knowledge of the system from the programmer in order to achieve good performance and scalability. Traditional parallel programming has been based on synchronization primitives such as barriers, critical sections and reader/writer locks, highly prone to programming errors. Transactional Memory (TM) is a relatively recent proposal that seeks to remove the synchronization problems from the programmer. However, many TM systems still rely on reader/writer locks, and would get benefited from an efficient implementation.

This thesis presents new hardware techniques to accelerate the execution of such parallel programs. We propose a Hybrid TM system based on reader/writer locks, which minimizes the software overheads when acceleration hardware is present, but still allows for correct software-only execution. The fairness of the system is studied, and a mechanism to guarantee fairness between hardware and software transactions is provided. We introduce a low-cost distributed mechanism named the Lock Control Unit to handle fine-grain reader-writer locks. Finally, we propose an organization of a parallel architecture based on Kilo-Instruction Processors, which helps to simplify the consistency model while allowing for high performance thanks to the speculative large instruction window.

#### **Table of Contents**

| ABSTRACT                                                                                | ]          |

|-----------------------------------------------------------------------------------------|------------|

| TABLE OF CONTENTS                                                                       | V          |

| LIST OF FIGURES                                                                         | IX         |

| LIST OF TABLES                                                                          | XI         |

| CHAPTER 1. INTRODUCTION                                                                 | 1          |

| 1.1. Shared-memory architectures                                                        | 4          |

| 1.1.1. Memory coherence                                                                 | 5          |

| 1.1.2. Memory consistency                                                               | $\epsilon$ |

| 1.2. Fundamentals of shared-memory parallel programming                                 | 8          |

| 1.2.1. Synchronization mechanisms                                                       | 8          |

| 1.2.1.1. Barriers                                                                       | 8          |

| 1.2.1.2. Locks and critical sections                                                    | g          |

| 1.2.2. Difficulties of parallel programming                                             | g          |

| 1.2.2.1. Scalability and critical sections                                              | g          |

| 1.2.2.2. Granularity                                                                    | 10         |

| 1.2.2.3. Deadlock                                                                       | 11         |

| 1.2.2.4. Priority inversion                                                             | 11         |

| 1.2.2.5. Starvation                                                                     | 12         |

| 1.2.2.6. Complexity of concurrent data structures                                       | 12         |

| 1.3. Locking mechanisms                                                                 | 14         |

| 1.3.1.1. Centralized vs. queue-based locking                                            | 14         |

| 1.3.1.2. Spin-locks vs. try-locks vs. blocking locks                                    | 15         |

| 1.3.1.3. Reader-writer locking                                                          | 16         |

| 1.3.1.4. Fairness issues                                                                | 17         |

| 1.3.1.5. Hierarchical lock implementations                                              | 18         |

| 1.3.1.6. Pathologies of locks                                                           | 19         |

| 1.3.1.6.1. Single-thread locking and biased locks                                       | 19         |

| 1.3.1.6.2. Waiting thread suspension in FIFO locks                                      | 20         |

| 1.3.1.6.3. Mostly Reader locking                                                        | 20         |

| 1.4. Fundamentals of Transactional Memory                                               | 21         |

| 1.4.1. Atomic sections                                                                  | 21         |

| 1.4.2. The ACID properties                                                              | 22         |

| 1.4.2.1. Atomicity                                                                      | 22         |

| 1.4.2.2. Consistency                                                                    | 23         |

| 1.4.2.3. Isolation                                                                      | 23         |

| 1.4.2.4. Durability                                                                     | 24         |

| 1.4.3. Programmability and composability 1.4.4. Update mechanism: In-place vs. deferred | 24         |

| 1.4.4. Opuale mechanism. M-place vs. deferred                                           | 25         |

vi · Table of Contents

| CHAPTER 2. LOCK-BASED HYBRID TRANSACTIONAL MEMORY                                  | 51              |

|------------------------------------------------------------------------------------|-----------------|

| 1.6.4. Microarchitectural improvements for performance, locking and consistency    | 49              |

| 1.6.3. HW acceleration of locking mechanisms                                       | 49              |

| 1.6.2. Fairness among software and hardware transactions                           |                 |

| ·                                                                                  | 48              |

| 1.6.1. Lock-based Hybrid TM                                                        | <b>48</b><br>48 |

| 1.6. Contributions of this thesis                                                  | 48              |

| 1.5.3.4. Load/store queue handling                                                 | 48              |

| 1.5.3.2. Bi-level issue queue 1.5.3.3. Ephemeral registers                         | 47<br>47        |

| 1.5.3.1. Checkpointing mechanism and early release                                 | 46              |

| 1.5.3. Kilo-instruction processor overview                                         | 46              |

| 1.5.2. Thread-level parallelism                                                    | 45              |

| -                                                                                  |                 |

| 1.5.1. Evolution of ILP-driven microarchitectural designs                          | 43              |

| 1.5. Processor microarchitecture and performance aspects                           | 43              |

| 1.4.13.2.2. Sun's Hybrid TM and Rock                                               | 42              |

| 1.4.13.2.1. Intel's Hybrid TM                                                      | 41              |

| 1.4.13.1.3. Hexible HW (HEXTW)  1.4.13.2. Hybrid TM                                | 41              |

| 1.4.13.1.3. Flexible TM (FlexTM)                                                   | 41              |

| 1.4.13.1.2. Signature-accelerated TM (SigTM)                                       | 40              |

| 1.4.13.1.1. Hardware-Accelerated TM (HATM)                                         | 40<br>40        |

| 1.4.13.1. Hardware-accelerated TM                                                  |                 |

| 1.4.12.4. Lock-based STMs 1.4.13. Hardware-software Transactional Memory           | 39<br>40        |

| 1.4.12.3. Fraser's OSTM                                                            | 38              |

| 1.4.12.2. Software Transactional Memory for Dynamic-Sized Data Structures          | 37              |

| 1.4.12.1. Software Transactional Memory by Shavit and Touitou                      | 37              |

| 1.4.12. Software Transactional Memory                                              | 36              |

| 1.4.11.4. Log-based Transactional Memory (LogTM)                                   | 36              |

| 1.4.11.3. Bulk Transactional Memory                                                | 35              |

| 1.4.11.2. Transactional Coherence and Consistency (TCC)                            | 35              |

| 1.4.11.1. Transactional Memory by Herlihy and Moss                                 | 34              |

| 1.4.11. Hardware Transactional Memory                                              | 34              |

| 1.4.10. Irrevocable transactions                                                   | 33              |

| 1.4.9. Nested transactions                                                         | 32              |

| 1.4.8.3. Lock-based TM                                                             | 32              |

| 1.4.8.2. Non-blocking TM                                                           | 31              |

| 1.4.8.1. Wait-free, lock-free, obstruction-free and blocking progress conditions   | 31              |

| 1.4.8. Progress conditions                                                         | 30              |

| 1.4.7.4. Software policies                                                         | 30              |

| 1.4.7.3. Requestor-waits policy                                                    | 29              |

| 1.4.7.2. Requestor-wins policy                                                     | 29              |

| 1.4.7.1. Abort-always policy                                                       | 29              |

| 1.4.7. Contention management                                                       | 28              |

| 1.4.6. Data validation and the privatization problem                               | 26              |

| 1.4.5. Conflict detection mechanism: Lazy vs. Eager, visible vs. invisible readers | 25              |

| 2.1. Advantages of reader-writer blocking TM          | 53  |

|-------------------------------------------------------|-----|

| 2.2. Base STM overview                                | 53  |

| 2.3. Acceleration opportunities with a generic HTM    | 57  |

| 2.3.1. Avoid locking                                  | 58  |

| 2.3.2. Read set removal                               | 61  |

| 2.3.3. Write set removal and in-place update          | 62  |

| 2.4. Evaluation                                       | 63  |

| 2.4.1. Evaluation infrastructure                      | 63  |

| 2.4.2. Simulated models                               | 64  |

| 2.4.3. Benchmarks                                     | 65  |

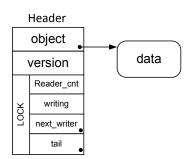

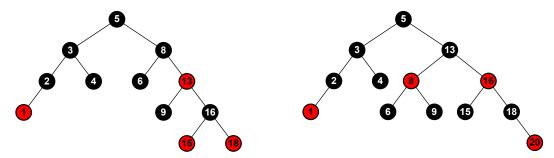

| 2.4.3.1. Red-black tree                               | 65  |

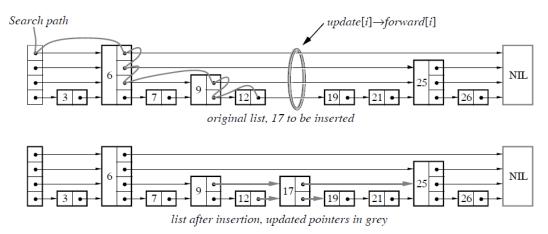

| 2.4.3.2. Skip-list                                    | 66  |

| 2.4.3.3. Hash table                                   | 67  |

| 2.4.4. Performance results                            | 67  |

| 2.4.4.1. Single-thread performance                    | 67  |

| 2.4.4.2. Read-only transactions                       | 68  |

| 2.4.4.3. Reader-writer transactions                   | 70  |

| 2.4.4.4. Number of HW retries in HW transactions      | 72  |

| 2.5. Summary                                          | 73  |

| CHAPTER 3. FAIRNESS IN HYBRID TRANSACTIONAL MEMORY    | 75  |

| 3.1. Writer starvation in Hybrid TM                   | 77  |

| 3.2. Directory reservations                           | 79  |

| 3.2.1. Issues with LogTM transactions                 | 80  |

| 3.2.2. Reservation Table and fair queuing             | 82  |

| 3.2.3. Thread de-scheduling and migration             | 83  |

| 3.3. Evaluation                                       | 84  |

| 3.3.1. Performance results                            | 85  |

|                                                       |     |

| 3.4. Summary                                          | 88  |

| CHAPTER 4. HW ACCELERATION OF LOCKING MECHANISMS      | 89  |

| 4.1. HW mechanisms for locking acceleration           | 91  |

| 4.2. The Lock Control Unit mechanism                  | 94  |

| 4.2.1. Hardware components                            | 95  |

| 4.2.1.1. The Lock Control Unit                        | 95  |

| 4.2.1.2. The Lock Reservation Table                   | 97  |

| 4.2.1.3. The Free Lock Table                          | 97  |

| 4.2.2. General overview                               | 98  |

| 4.2.2.1. Programming interface                        | 98  |

| 4.2.2.2. Two locking modes                            | 99  |

| 4.2.2.2.1. Queue-based locking                        | 100 |

| 4.2.2.2. Overflowed locking                           | 100 |

| 4.2.2.3. Write-lock acquisition, transfer and release | 100 |

| 4.2.2.4. Reader locking                               | 103 |

| 4.2.2.5. The Free Lock Table                                                  | 105 |

|-------------------------------------------------------------------------------|-----|

| 4.2.3. Detailed overview                                                      | 106 |

| 4.2.3.1. Design invariants                                                    | 106 |

| 4.2.3.2. LRT detailed overview                                                | 107 |

| 4.2.3.3. LCU state machine                                                    | 109 |

| 4.2.3.4. Communication primitives                                             | 110 |

| 4.2.3.5. Thread suspension and migration                                      | 111 |

| 4.2.3.6. Types of LCU entries and forward progress                            | 112 |

| 4.2.3.7. Management of LCU overflow                                           | 114 |

| 4.2.3.8. LRT overflow                                                         | 116 |

| 4.2.3.9. Read-only locking                                                    | 116 |

| 4.2.3.10. Hierarchical Locking                                                | 118 |

| 4.2.3.11. Paging, virtualization and process faulting issues                  | 119 |

| 4.3. Evaluation                                                               | 122 |

| 4.3.1. Number of messages in the critical path of lock transfer               | 123 |

| 4.3.2. Lock transfer time                                                     | 124 |

| 4.3.3. Fine-grain locking: STM benchmarks                                     | 127 |

| 4.3.4. Traditional parallel benchmarks                                        | 129 |

| 4.4. Summary                                                                  | 130 |

| CHAPTER 5. IMPLICIT TRANSACTIONAL MEMORY                                      | 133 |

| 5.1. Atomic sections and processor checkpointing                              | 135 |

| 5.1.1. Implementation details of implicit transactions                        | 136 |

| 5.1.2. Implicit transaction length and performance                            | 139 |

|                                                                               |     |

| 5.2. Sequential consistency with implicit transactions                        | 141 |

| 5.3. Lock speculation with implicit transactions                              | 143 |

| 5.3.1. Dependencies through locks and critical section speculation            | 144 |

| 5.3.2. Critical section speculation with software locks                       | 145 |

| 5.3.3. Critical section speculation with the LCU model                        | 147 |

| 5.3.3.1. Implicit transactions and ordinary LCU access                        | 147 |

| 5.3.3.2. Speculation support in the LCU                                       | 148 |

| 5.3.3.3. Implicit transactions and speculative LCU access                     | 150 |

| 5.3.3.4. Speculative LCU accesses and HyTM                                    | 151 |

| 5.4. Speculation beyond flags and barriers                                    | 151 |

| 5.5. Summary                                                                  | 152 |

| CHAPTER 6. CONCLUSIONS                                                        | 155 |

| 6.1. Contributions                                                            | 157 |

| 6.2. Future work                                                              | 159 |

| 6.3. Publications                                                             | 159 |

| 6.3.1. HyTM, kilo-instruction architectures and reader/writer synchronization | 160 |

| 6.3.2. Interconnection Networks                                               | 160 |

| CHAPTER 7. REFERENCES                                                         | 163 |

### **List of Figures**

| Figure 1-1: Example of a consistency problem. Initially $A = B = 0$ . Can $P_2$ load 0 from $A$ ? | . 7 |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 1-2: Example of data race                                                                  | . 8 |

| Figure 1-3: Example of the usage of a lock                                                        | . 9 |

| Figure 1-4: Coarse (left) vs fine (right) grain locking                                           | 10  |

| Figure 1-5: Necessity of acquiring multiple locks to avoid concurrency problems, from [71] ?      | 13  |

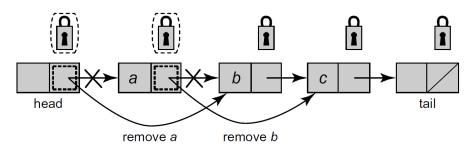

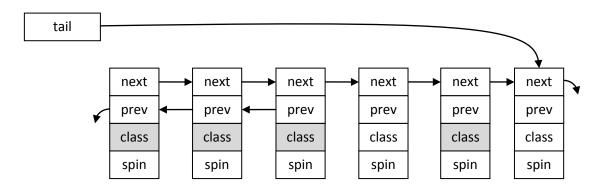

| Figure 1-6: Example of the MCS lock structure                                                     | 15  |

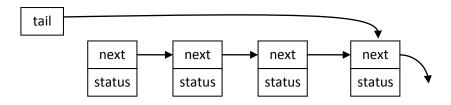

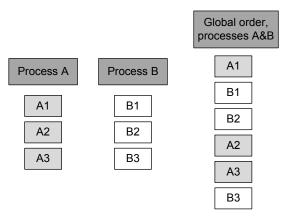

| Figure 1-7: Example of the MCS reader-writer lock structure. Grey fields represent readers        | 16  |

| Figure 1-8: Example of the Krieger et al. reader-writer lock. Grey fields are readers             | 17  |

| Figure 1-9: Incorrect implementation of a barrier using reader-writer locks                       | 18  |

| Figure 1-10: Example of code that fails in the privatization problem                              | 27  |

| Figure 1-11: Example of code that fails in the publication problem                                | 28  |

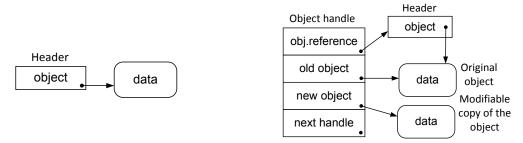

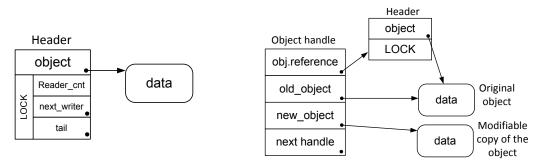

| Figure 1-12: Object structure in DSTM                                                             | 38  |

| Figure 1-13: Object structure (left) and object handle in the write-set list (right) of Frase     | r's |

| OSTM                                                                                              | 38  |

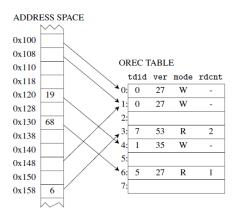

| Figure 1-14: Orec organization in the word-based STM by Harris and Fraser, taken from [64].       | 39  |

| Figure 1-15: Orec table in the HyTM system by Damron et al., taken from [33]                      | 42  |

| Figure 1-16: Block diagram of an out-of-order superscalar processor                               | 44  |

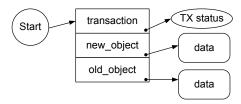

| Figure 2-1: STM programmer interface                                                              | 54  |

| Figure 2-2: STM Object structure (left) and read/write set list element (right)                   | 54  |

| Figure 2-3: Three steps in a commit of a binary tree data structure. The intermediate step        | b)  |

| contains a cycle, what can lead to zombie transactions that never commit                          | 56  |

| Figure 2-4: Modified STM lock structure for HT Txs to detect conflicts with writing SW Txs        | 59  |

| Figure 2-5: Lock implementation in the HyTM model                                                 | 60  |

| Figure 2-6: Modified STM Object with a version field allowing for in-place updates                | 62  |

| Figure 2-7: Left, Red-Black tree example. Right, status after the addition of node 20             | 65  |

| Figure 2-8: Skip-list example, taken from [116]                                                   | 66  |

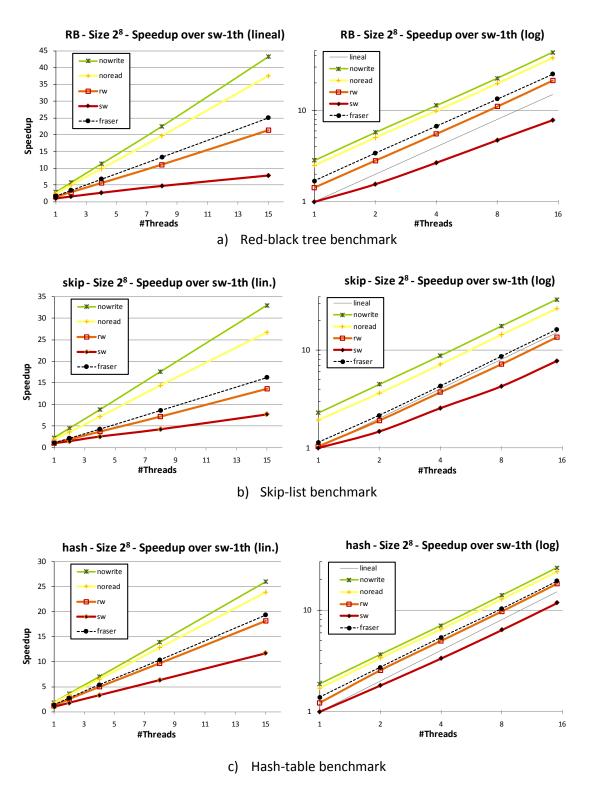

| Figure 2-9: RB, skip and hash speedup with read-only transactions, $k = 8$ , in linear (left) as  | nd  |

| logarithmic (right) scales                                                                        | 59  |

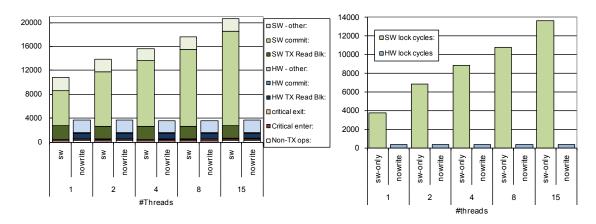

| Figure 2-10: Left: RB cycle dissection, p=0, k=8. Right: Cycles in lock accesses                  | 70  |

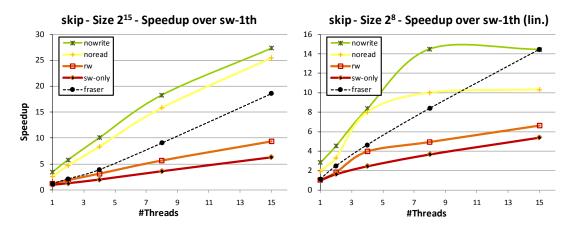

| Figure 2-11: Skip-list performance under low (left) and high (right) contention, $p = 10\%$       | 71  |

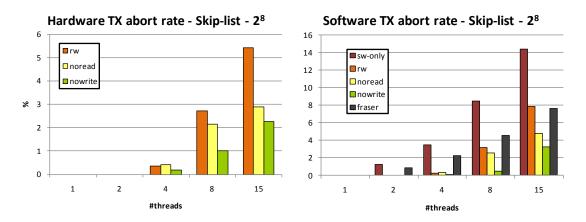

| Figure 2-12: Transactions aborted in HW and SW modes. Skip list with k=8, p=10%                   | 71  |

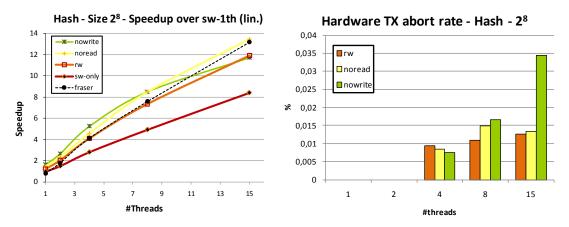

| Figure 2-13: Hash-table speedup and abort rate with k=8, p=25% (high contention)                  | 72  |

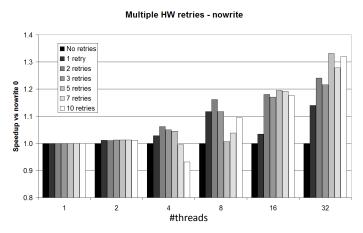

| Figure 2-14: Performance with different number of HW retries of aborted transactions              | 72  |

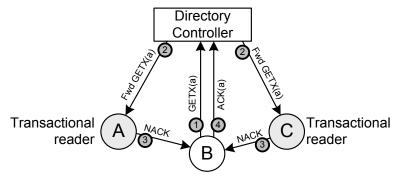

| Figure 3-1: Example of NACK messages in LogTM. Proc. B requests the memory location               | a,  |

| which has been read by processors A and C                                                         | 78  |

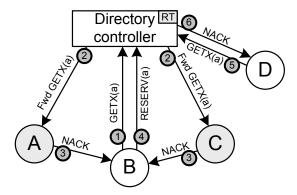

| Figure 3-2: Pathological example of transactional code that stalls due to writer starvation       | 78  |

| Figure 3-3: Message transfer with the Reservation Table mechanism                                   | 79    |

|-----------------------------------------------------------------------------------------------------|-------|

| Figure 3-4: Reservation Table structure                                                             | 80    |

| Figure 3-5: Message transfer with the Reservation Table mechanism                                   | 81    |

| Figure 3-6: Message transfer with the Reservation Table mechanism                                   | 83    |

| Figure 3-7: Normalized execution time of the RB benchmark, k=11, p=10%                              | 86    |

| Figure 3-8: Normalized execution time of Hash and skip, k=11                                        | 87    |

| Figure 4-1: Lock Control Unit architecture                                                          | 95    |

| Figure 4-2: Contents of each LCU entry                                                              | 96    |

| Figure 4-3: Contents of each LRT entry. The $Tail_{id}$ field's composition is equal to $Head_{id}$ | 97    |

| Figure 4-4: Contents of each FLT entry                                                              | 97    |

| Figure 4-5: Functions for lock acquisition and release                                              | 99    |

| Figure 4-6: Lock acquisition when the lock is free                                                  | . 101 |

| Figure 4-7: Enqueue when the taken lock is uncontended. $LCU_0$ is the current owner                | . 101 |

| Figure 4-8: Lock transfer                                                                           | . 102 |

| Figure 4-9: Possible data race in the notification mechanism                                        | . 103 |

| Figure 4-10: Example of concurrent read locking                                                     | . 104 |

| Figure 4-11: Races in the enqueue process                                                           | . 108 |

| Figure 4-12: Simplified state machine of the LCU entries                                            | . 110 |

| Figure 4-13: Detailed state machine of the LCU entries                                              | . 110 |

| Figure 4-14: Example of migration. Thread $t_2$ migrates from processor 2 to 9 while waiting.       | . 112 |

| Figure 4-15: Example of read-only locking                                                           | . 117 |

| Figure 4-16: Sketch of a hierarchical implementation                                                | . 119 |

| Figure 4-17: CS execution time including lock transfers. SSB vs LCU                                 | . 125 |

| Figure 4-18: CS execution time including lock transfers. LRT vs software locks                      | . 126 |

| Figure 4-19: Transaction cycle dissection of the RB benchmark with 2 <sup>8</sup> max. nodes        | . 127 |

| Figure 4-20: Transaction execution time, 16 threads and 75% of read-only transactions               | . 128 |

| Figure 4-21: Application execution time                                                             | . 129 |

| Figure 5-1: Execution flow example with 4 processors                                                | . 137 |

| Figure 5-2: Estimation of the proportion of rollbacks in SPLASH                                     | . 140 |

| Figure 5-3: Sequentially consistent reordering of memory operations from 2 processors               | . 142 |

| Figure 5-4: Sequentially consistent reordering of checkpoints from 2 processors                     | . 142 |

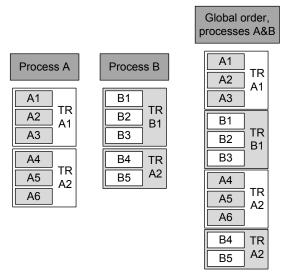

| Figure 5-5: Different checkpointing schemes with critical sections                                  | . 144 |

| Figure 5-6: Examples of critical sections that often admit parallel execution, from [118]           | . 145 |

| Figure 5-7: Example of speculative access to a lock                                                 | . 149 |

| Figure 5-8: Deallocation of speculative entries in the lock queue                                   | . 150 |

#### **List of Tables**

| Table 2-1: Summary of operations when conflicts occur in the HyTM                     | 61    |

|---------------------------------------------------------------------------------------|-------|

| Table 2-2: Single thread normalized performance (inverse of the transaction run time) | 68    |

| Table 4-1: Comparative of SW and HW locking mechanisms                                | 94    |

| Table 4-2: Possible states of a LCU entry                                             | 96    |

| Table 4-3: Communication primitives                                                   | . 111 |

# **Chapter 1.** Introduction

The free lunch is over [148]. The traditional evolution that processor microarchitectures had followed during the last 20 or more years, based on higher processor frequencies, wider instruction windows and deeper instruction pipelines, is over. The current technological constraints, mainly the power wall and the memory wall, make such design lead to diminishing returns. Therefore, most processor architects have moved to Chip Multiprocessor (CMP) designs that rely on an increase of the number of processing cores, but not on their individual performance. This makes that traditional, single threaded programs, do not perform better with new generations of processors. Programmers cannot rely on the technological advances to make their simple code run faster; they must use a parallel programming model to exploit the system capabilities.

Parallel programming makes use of multiple tasks running simultaneously on multiple processors, making a joint effort to complete the execution faster. Such design involves many difficulties, both in the hardware side (how to design a parallel machine) and in the software side (how to efficiently program such parallel machine). Even more, both hardware and software interact with each other, so the design of a given layer is dependent on the design of the rest of the system. This introductory Chapter will detail the main problems of parallel programming and the issues of designing parallel machines, along with the related work that targets these problems. Specifically, it introduces the main difficulties of parallel programming, with a special focus on synchronization mechanisms; recent proposals on Transactional Memory that try to simplify the programming models; and technological and architectural aspects than condition the design of current parallel systems. All these aspects are the base for the subsequent work developed in this thesis.

There are two basic models for parallel programming. The message-passing paradigm, for example implemented in MPI [151], requires the programmer to explicitly declare each communication primitive used to communicate the processors. The shared-memory paradigm, by contrast, provides a shared address space that can be accessed by all of the processes, or "threads", which are implemented for example using the POSIX standard [1]. The communication between threads occurs through shared variables, which in turn rely on the

underlying architecture providing the necessary coherence and consistency mechanisms to send the required messages. However, in this case the communication burden is hidden from the programmer.

Parallel programming is inherently more difficult than serial programming. In a parallel program, the different tasks have to synchronize with each other to access the data to be processed (data partitioning) and communicate intermediate results (data sharing), all of it synchronizing the different execution phases (synchronization, involving task creation and termination). Debugging is also more complex than in serial programming, since the execution is not deterministic, depending on the relative speed of the different tasks. Finally, the architectural implementation can impose additional restrictions that the programmer or compiler must consider. Shared-memory machines often implement relaxed memory models that provide higher performance but require of explicit fences and synchronization instructions. Section 1.1 details the design issues and performance implications of different coherence and consistency models. Section 1.2 gives deeper insight into the problems and difficulties of parallel programming on a shared-memory architecture. One of the basic tools used for mutual exclusion are locks, which are further studied in section 1.3.

Transactional Memory (TM) [70] pretends to simplify some of the difficulties of parallel programming. By providing the abstraction of a database *transaction* to the programmer, the problem of mutual exclusion is highly simplified. Multiple hardware TM (HTM) and software TM (STM) systems have been proposed, with different benefits and weaknesses. Also, Hybrid TM (HyTM) systems try to get an efficient implementation with low hardware costs. They are introduced in detail in section 1.4.

This Chapter will also deal with the microarchitectural issues that arise when designing a high performance parallel system. The evolution in microarchitecture design leading to diminishing returns in single-processor designs, and the current performance issues are discussed in section 1.5. This section also presents an introduction of the Kilo-Instruction Processor architecture that is the base for the last Chapter of this thesis.

Finally, this introductory Chapter is concluded with a summary of the contributions presented in this thesis, in section 1.6.

# 1.1. Shared-memory architectures

Shared-memory parallel machines provide a single physical view of the memory for all the processors. On these machines, different concurrent tasks of the same process, named threads, can communicate with each other by merely reading and writing memory locations. By contrast, on a distributed-memory machine, each processor has its own memory and different tasks working on the same program must communicate to each other by explicitly sending messages with data o synchronization. This thesis focuses on shared-memory machines.

Shared-memory architectures must provide the same view of the memory for all the processors in the system. This might be simple in a model that does not use data caches, in which all processors access the same shared memory controller. However, most systems have two or more levels of caches to reduce the performance penalty of the distant memory (in terms of processor cycles to access data). This allows for the concurrent existence of multiple copies of the same data block, what imposes coherence and consistency problems, detailed next.

# 1.1.1. Memory coherence

In a shared-memory system multiple processors can access the same block with read and write operations. This will generate multiple copies of the block in the different data caches, with multiple versions of the data as the writes occur. Informally, a coherence mechanism deals with the delivery of a valid version of the data to each request.

A formal definition can be taken from [68]. A memory system is coherent if:

- 1. A read by a processor  $P_1$  to a location A that follows a write by  $P_1$  to A, with no writes of A by another processor occurring between the write and the read by  $P_1$ , always returns the value written by  $P_1$ .

- 2. A read by a processor to location *A* that follows a write by another processor to *A* returns the written value if the read and write are sufficiently separated in time and no other writes to *A* occur between the two accesses.

- 3. Writes to the same location are *serialized*; that is, two writes to the same location by any two processors are seen in the same order by all processors. For example, if the values 1 and then 2 are written to a location, processors can never read the value of the location as 2 and then later read it as 1.

Multiple coherence protocols have been developed, both in hardware and in software. A good survey can be found in [146]. Most machines nowadays implement hardware coherence, but others, such as the Cell processor [73], implement coherence between the main processor and the SPE units in software, requiring the programmer to reason about what is shared in each processing element.

According to their implementation, there are typically two classes of coherence protocols: bus based or directory based. Bus-based systems can rely on a *snoopy* protocol. All the processors "snoop" a centralized bus and detect other processors' requests and updates. This allows them to respond to memory requests if they have the block of data in their local caches, rather than waiting for the long-latency main memory access. Similarly, it allows them to detect conflicts with the memory writes from other processors, updating or invalidating their local caches. By contrast, directory based protocols can be implemented in a distributed manner, such as in the

DASH multiprocessor [91]. The directory contains metadata about the sharers of each block, and possibly about an owner who contains an updated version. Directory-based protocols are implemented with coherence messages, which are sent from one element to another to invalidate sharers upon a write, propagate updated versions of a block upon a read, and so on.

The caches in a coherent system implement a state machine with several possible states, typically all or part of the MOESI states [149]. These states differ on their exclusiveness and ownership, as follows:

- a) Modified (M), the cache contains the only valid copy of the data, which is dirty: the values in main memory have not been updated yet.

- b) Owned (O), the cache contains a dirty copy of the data, with the main memory not yet updated. However, this copy is not exclusive; other caches can have the same block in shared state. The only owner is responsible for the block, meaning that any request in the directory will be forwarded to the owner, who serves the request.

- c) Exclusive (E), the cache is the only one in the system with a valid and clean copy of the block.

- d) Shared (S), the cache contains a valid copy of the block, which can be also present in other caches.

- e) Invalid (I), not present in the cache or invalidated by a coherence request, such as a remote write.

Different implementations are typically identified with the subset of these states that are used, for example, MESI, MOSI or MSI. Additionally, a real protocol requires multiple transient states, to support the races that occur when multiple processors request a block concurrently with different access modes. This makes coherence protocols very complex and difficult to validate. Recent proposals such as [102] focus on simplifying the verifiability of the coherence mechanism, while they preserve the presented valid states.

#### 1.1.2. Memory consistency

The memory consistency model (or, simply, the memory model) manages the correct ordering of memory operations to different memory locations. While the coherence protocol has to propagate the updates performed on memory locations to all of the required processors, the consistency model specifies the timing of such update.

Let us consider the example case of two processors  $P_1$  and  $P_2$  in a coherent system, accessing a memory location A with an initial value of  $a_0$ . A write from  $P_1$  updates A from  $a_0$  to  $a_1$ . What happens with subsequent reads to A? By the first condition of the coherence,  $P_1$  must read the updated value  $a_1$ . However,  $P_2$  can continue accessing its locally cached entry with the old

value  $a_0$  for a certain time before the updated value is propagated, and still obey the second condition of the coherence mechanism. This case would be a coherent system, with a relaxed consistency model.

The different observed data can be especially important when multiple memory locations are involved and  $P_1$  and  $P_2$  use one of them to synchronize with each other. Consider the example in Figure 1-1 in which processor  $P_1$  updates the data in A (instruction 1) and then sets a flag in B to notify processor  $P_2$  that the data is ready (instruction 2). What happens if the update of the flag in B propagates to  $P_2$  before the update of the data in A?  $P_2$  will access the old data 0 in A, considering it as the new one, what can lead to an unexpected program behavior. Observe that the problem in this case is not a coherence or architectural problem, but the programmer (or the compiler) not obeying to the consistency model restrictions, which would typically require of an especial *fence* instruction between instructions 1 and 2 from  $P_1$  to make sure that all data are correctly propagated. Several examples of possible problems with a relaxed model, along with a detailed study of multiple consistency models, can be found in [5].

|    | Processor P <sub>1</sub> | Processor P <sub>2</sub> |  |

|----|--------------------------|--------------------------|--|

| 1: | st & <i>A</i> , 10       | beq & <i>B</i> , 0, -4   |  |

| 2: | st & <i>B</i> , 1        | ld & <i>A</i> , r1       |  |

Figure 1-1: Example of a consistency problem. Initially A = B = 0. Can  $P_2$  load 0 from A?

Sequential Consistency (SC) [87] is the most desirable model since it provides the most intuitive programming model. SC requires that the result of any execution be the same as if the memory accesses executed by each processor were kept in order, and the accesses among different processors were arbitrarily interleaved. This is what any programmer would intuitively consider to be the 'common' behavior of a multiprocessor system if not aware of what a memory model is. The problem with SC is that it most often requires that memory operations from each program appear to be executed in-order, what may limit the system performance. Write buffers, multiple memory controllers or an unordered interconnect raise issues with possible races and might not be used in a system obeying SC.

Other consistency models such as Total Store Order (TSO, [141], used in Sparc machines among others) or Processor Consistency (PC, [54], used in the x86 architecture and others) achieve a higher performance by relaxing these constraints, at the cost of a more complex programming framework. These models typically allow a processor to observe its own writes before they are sent to the rest of the processors, what allows for significant optimizations while still providing a quite intuitive memory model. More relaxed models, such as Relaxed Consistency (RC, [51]) allow further interleaving of writes from different processors.

Contrary to coherence, the consistency model is visible to the programmer. Hill [72] argues for simple consistency models such as SC, despite its lower performance, to prevent difficult-to-

find consistency problems. Besides, speculative execution [52] has been proven to allow for simple consistency models with a similar performance to the relaxed ones.

# 1.2. Fundamentals of shared-memory parallel programming

Shared-memory parallel programs make use of multiple concurrent threads, provided by a system library. Typically, the implementation will be specific to the operating system (such as Linux, Solaris or Windows threads) or follow the portable standard POSIX [1]. Such implementation will define, among others, the tasks of creating new threads, synchronizing their operations and terminating them. This section is focused on the synchronization mechanisms.

# 1.2.1. Synchronization mechanisms

The access to shared data must be protected to prevent different threads from updating the same value, overwriting each other's modifications, without notice. An example is presented in Figure 1-2: The increase of the variable a in C code is translated to three ISA instructions. In the example execution presented on the right, a is initially 0. Two threads run the same increase function, but a finishes being 1, not 2. The problem is that the update of the memory location is not atomic; instead, both threads read the same initial value 0 (at time 1 and 2), and write the same updated value 1 (time 4 and 5).

| <u>C code</u> <u>Assembler code</u>    | 2  | <u>Execution</u> |              |  |

|----------------------------------------|----|------------------|--------------|--|

| void increase(&a){ Id &a, I1           |    | Thread 1         | Thread 2     |  |

| a = a + 1; addi l1,1,l2<br>} st l2, &a | 1: | ld &a, l1        |              |  |

| , 30.2, 33                             | 2: |                  | ld &a, l1    |  |

|                                        | 3: | addi l1,1,l2     | addi l1,1,l2 |  |

|                                        | 4: | st I2, &a        |              |  |

|                                        | 5: |                  | st I2, &a    |  |

Figure 1-2: Example of data race

To overcome such problems, a proper synchronization mechanism among threads is required. There are two classic means of synchronization to overcome such problems: First, barriers can divide execution into different phases of executions in which each thread only accesses an assigned, individual data set. Second, locks are used to block a memory location or code section, reserving it for a given thread. They are presented in the next sections.

#### 1.2.1.1. Barriers