Grado en Ingeniería de Tecnologías de Telecomunicación. Electrónica Digital I. Problemas resueltos. Tema IIIb.

Página 1. Diseñar un circuito multiplexor con prioridad de 4 bits. El circuito tiene 4 entradas de datos (I3-I0), 4 entradas de selección (S3-S0) y dos salidas Z y G. Cuando una o más de las entradas S están a 1, Z toma el valor de la entrada Ii, siendo i es el índice más alto de las entradas Si que están a 1; si todas las entradas S3-S0 están a 0, entonces Z toma el valor 0. La salida G se fija a 1 si al menos alguna entrada Si está a 1, en caso contrario se fija a 0.

- a) Mostrar en una tabla el comportamiento lógico del circuito. Encontrar las ecuaciones lógicas de las salidas Z y G expresándolas en dos niveles y en forma factorizada.

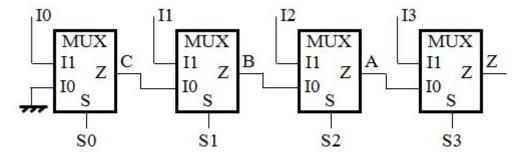

- b) Implementar la expresión factorizada de Z utilizando multiplexores de 2 entradas.

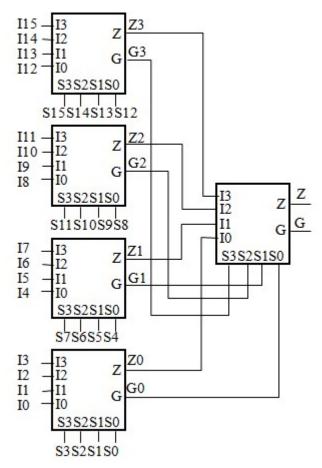

- c) Diseñar un multiplexor con prioridad de 16 bits en base a los multiplexores con prioridad de 4 bits diseñados.

- d) Realizar una descripción VHDL del multiplexor con prioridad.

- a) El multiplexor con prioridad sigue esta tabla, donde se muestran las condiciones en las entradas S para que cada una de las entradas I pase a la salida.

| Función                                                                | <b>S3</b> | S2 | S1 | S0 | Z  | G |

|------------------------------------------------------------------------|-----------|----|----|----|----|---|

| S3 I3                                                                  | 1         | X  | X  | X  | I3 | 1 |

| <del>S3</del> S2 I2                                                    | 0         | 1  | X  | X  | I2 | 1 |

| <u>\$3</u> \$2 \$1 I1                                                  | 0         | 0  | 1  | X  | I1 | 1 |

| <u>\$3</u> <u>\$2</u> <u>\$1</u> \$0 10                                | 0         | 0  | 0  | 1  | Ι0 | 1 |

| $\overline{S3}  \overline{S2}  \overline{S1}  \overline{S0} \bullet 0$ | 0         | 0  | 0  | 0  | 0  | 0 |

De la tabla genero Z y la factorizo:

$$Z = S3 I3 + \overline{S3} S2 I2 + \overline{S3} \overline{S2} S1 I1 + \overline{S3} \overline{S2} \overline{S1} S0 I0$$

$Z = S3 I3 + \overline{S3} (S2 I2 + \overline{S2} S1 I1 + \overline{S2} \overline{S1} S0 I0)$

$Z = S3 I3 + \overline{S3} [S2 I2 + \overline{S2} (S1 I1 + \overline{S1} S0 I0)]$

También se ve intuitivamente de la tabla (G es 1 si alguna de las entradas S es 1, y 0 si no lo es ninguna) que:

$$G = S3 + S2 + S1 + S0$$

b) Los multiplexores de 2 entradas siguen la expresión  $Z = S I1 + \overline{S} I0$ . De la expresión factorizada de Z todos los paréntesis guardan la relación de un multiplexor de dos entradas, salvo el paréntesis más interno, que se puede modificar para que lo cumpla.

$$Z = S3 I3 + \overline{S3} A$$

$A = S2 I2 + \overline{S2} (S1 I1 + \overline{S1} S0 I0) = S2 I2 + \overline{S2} B$

$B = S1 I1 + \overline{S1} S0 I0 = S1 I1 + \overline{S1} C$

$C = S0 I0 = S0 I0 + \overline{S0} \bullet 0$

Con lo que se puede diseñar este circuito:

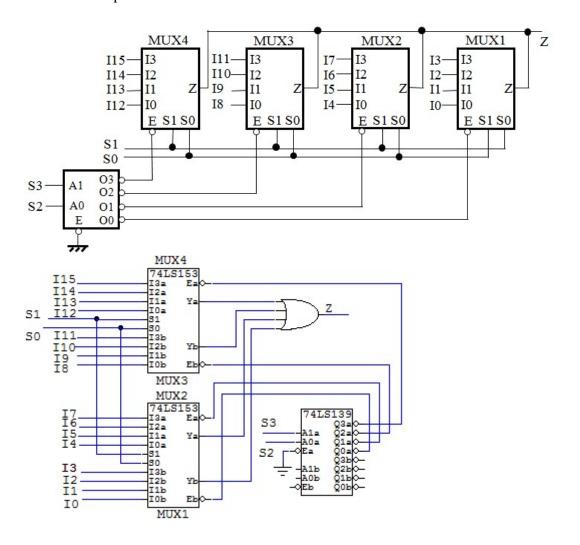

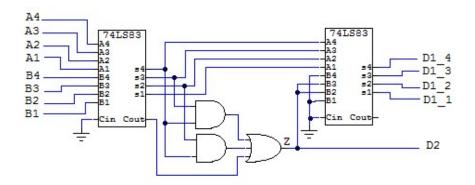

c) Para generar un circuito multiplexor con prioridad de 16 bits con multiplexores con prioridad de 4 bits, hay que usar un circuito como el de la figura. En la figura los 16 bits se dividen en grupos de 4 ordenados de mayor a menor, tanto las entradas I como las entradas S, con lo que se usan 4 multiplexores con prioridad de 4 bits. Se necesita un quinto multiplexor para general la salida final, el multiplexor de la derecha en la figura.

Si alguna de las entradas S15-S12 está a 1 entonces su G (G3) es 1, con lo que el quinto multiplexor tiene su S3 a 1, por lo que Z es su I3, que es Z3, donde Z3 es una de las entradas I15-I12, dependiendo de la entrada de índice más alto a 1 en S15-S12. Si ninguna de las entradas S15-S12 están a 1, entonces G3 es 0, y habría que mirar el resto de las entradas, empezando por S11-S8, repitiendo el funcionamiento anterior con Z2 y G2. Similarmente si S11-S8 son 0, se comprueban S7-S3 (Z1 y G1), y si estas son 0 se comprueba S3-S0 (Z0 y G0). Si todas las entradas S son 0, en el quinto multiplexor todas las entradas S son 0s, por lo que Z es 0.

d) Primero hago una descripción VHDL específica para el problema de 4 bits basada en una sentencia del tipo *if-elsif-else*. Hago una segunda descripción genérica para cualquier número de bits, donde uso sentencias VHDL no vistas en las clases teóricas: la sentencia *exit* en un *for*

permite abandonar el lazo sin recorrerlo entero. Esta descripción genérica podría hacerse también sin recurrir a estas sentencias, usando variables extras de control. En la descripción genérica inicializo primero las salidas Z y G a 0, y luego las modifico si alguna de las entradas S está a 1.

```

library ieee;

use ieee.std logic 1164.all;

entity muxconpri4 is

port( S, I: in std_logic_vector(3 downto 0);

2, G: out std logic );

end muxconpri4;

architecture uno of muxconpri4 is

begin

process(S, I)

begin

if ( S(3) = '1' ) then

Z <= I(3); G <= '1';

elsif (S(2) = '1') then

Z <= I(2); G <= '1';

elsif ( S(1) = '1' ) then

Z <= I(1); G <= '1';

elsif ( S(0) = '1' ) then

Z <= I(0); G <= '1';

else Z <= '0'; G <= '0';

end if;

end process;

end uno;

```

```

library ieee;

use ieee.std_logic_1164.all;

entity muxconprigen is

generic (N: integer := 4);

port( S, I: in std_logic_vector(N-1 downto 0);

Z, G: out std logic );

end muxconprigen;

architecture uno of muxconprigen is

process(S, I)

begin

Z <= '0'; G <= '0';

for j in N-1 downto 0 loop

if ( S(j) = '1' ) then

Z <= I(j); G <= '1';

exit; -- Finaliza el lazo si hay 1 en S

end if;

end loop;

end process:

end uno:

```

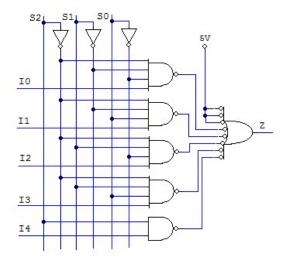

Página 2-1. Construir un multiplexor de 5 entradas a) utilizando puertas lógicas.

b) utilizando multiplexores de dos entradas.

Supongo un multiplexor de 5 entradas, numeradas de I0 a I4. Para controlar las 5 entradas se necesitan 3 entradas de selección (S2 S1 S0), capaces de codificar de 0 (000) a 4 (100). Inicialmente la tabla del problema queda:

| Función                          | S2 | S1 | S0 | Z  |

|----------------------------------|----|----|----|----|

| <u>S2</u> <u>S1</u> <u>S0</u> I0 | 0  | 0  | 0  | I0 |

| <u>\$2</u> \$1 \$0 I1            | 0  | 0  | 1  | I1 |

| <u>\$2</u> \$1 <u>\$0</u> I2     | 0  | 1  | 0  | I2 |

| <u>\$2</u> \$1 \$0 I3            | 0  | 1  | 1  | I3 |

| S2 <u>S1</u> <u>S0</u> I4        | 1  | 0  | 0  | I4 |

Pero si nos fijamos en que la última entrada es la única fila que tiene S2 a 1, la tabla puedo definirla como:

| Función                      | S2 | S1 | S0 | Z         |

|------------------------------|----|----|----|-----------|

| <u>S2 S1 S0</u> I0           | 0  | 0  | 0  | 10        |

| <u>\$2</u> \$1 \$0 I1        | 0  | 0  | 1  | I1        |

| <u>\$2</u> \$1 <u>\$0</u> 12 | 0  | 1  | 0  | I2        |

| <u>\$2</u> \$1 \$0 I3        | 0  | 1  | 1  | I3        |

| S2 I4                        | 1  | X  | X  | <u>I4</u> |

a) La función lógica de Z puede obtenerse directamente de la tabla anterior, sin realizar ninguna simplificación, e implementarla con puertas lógicas (NAND en la figura).

$$Z = \overline{S2} \overline{S1} \overline{S0} \overline{I0} + \overline{S2} \overline{S1} \overline{S0} \overline{I1} + \overline{S2} \overline{S1} \overline{S0} \overline{I2} + \overline{S2} \overline{S1} \overline{S0} \overline{I3} + \overline{S2} \overline{I4}$$

**b)** La función del apartado a) puede operarse de forma que las expresiones queden del tipo  $S I1 + \overline{S} I0$ , que corresponden a multiplexores de dos entradas.

$$Z = S2 I4 + \overline{S2} (\overline{S1} \overline{S0} I0 + \overline{S1} S0 I1 + S1 \overline{S0} I2 + S1 S0 I3) =$$

=  $S2 I4 + \overline{S2} [S1 (S0 I3 + \overline{S0} I2) + \overline{S1} (S0 I1 + \overline{S0} I0)]$

Con lo que uso los siguientes cuatro multiplexores de dos entradas y genero el circuito con multiplexores de dos entradas.

$$Z = S2 I4 + \overline{S2} A$$

$$A = S1 B + \overline{S1} C$$

$$B = S0 I3 + \overline{S0} I2$$

$$C = S0 I1 + \overline{S0} I0$$

$$I3 - \overline{I1} Z$$

$$I1 Z$$

$$I2 - \overline{I0} S$$

$$I1 - \overline{I1} Z$$

$$I1 Z$$

$$I0 - \overline{I0} S$$

$$S0$$

$$S0$$

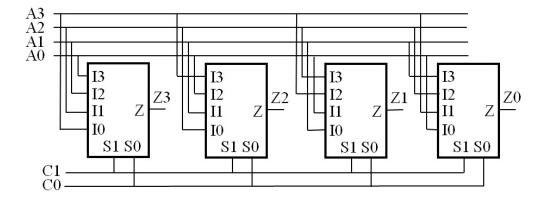

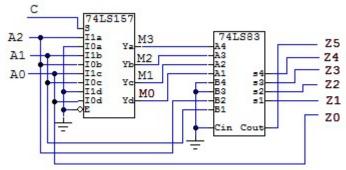

Página 2\_2. Un circuito de "desplazamiento en barril" ("barrel-shifter") mueve los datos de entrada de forma que aparezcan en la salida girados el número de posiciones marcados por las señales de control. Construir utilizando multiplexores un "barrel-shifter" de 4 bits de entrada (a3a2a1a0) y 4 bits de salida (z3z2z1z0) con 4 posibles desplazamientos (dos señales de control c1c0):

```

(c1c0) = 0 \Rightarrow (z3z2z1z0) = (a3a2a1a0),

(c1c0) = 1 \Rightarrow (z3z2z1z0) = (a2a1a0a3),

(c1c0) = 2 \Rightarrow (z3z2z1z0) = (a1a0a3a2),

(c1c0) = 3 \Rightarrow (z3z2z1z0) = (a0a3a2a1).

```

Realizar la descripción VHDL de este circuito.

Del enunciado se puede obtener la operación de las 4 salidas, comparadas con el funcionamiento de un multiplexor de cuatro entradas, suponiendo que las entradas de control C1 y C0 se conectan directamente a las entradas de selección C1 y C0 del multiplexor. Cada salida Z puede ser implementada con un multiplexor de 4 cuyas correspondientes entradas I0, I1, I2 y I3 se conectan a las entradas A indicadas en la tabla.

| S1 | S0 | Z  | <b>C1</b> | C0 | <b>Z</b> 3 | <b>Z2</b> | <b>Z</b> 1 | <b>Z</b> 0 |

|----|----|----|-----------|----|------------|-----------|------------|------------|

| 0  | 0  | I0 | 0         | 0  | A3         | A2        | A1         | A0         |

| 0  | 1  | I1 | 0         | 1  | A2         | A1        | A0         | A3         |

| 1  | 0  | I2 | 1         | 0  | A1         | A0        | A3         | A2         |

| 1  | 1  | I3 | 1         | 1  | A0         | A3        | A2         | A1         |

La descripción VHDL puede ser:

```

library ieee;

use ieee.std logic 1164.all;

entity barrel is

port (A: in std logic vector (3 downto 0);

C: in std_logic_vector(1 downto 0);

Z: out std logic vector(3 downto 0) );

end barrel;

architecture uno of barrel is

begin

process (A, C)

begin

case C is

when "00" => Z <= A;

when "01" => Z <= A(2 downto 0) & A(3);

when "10" \Rightarrow Z \Leftarrow A(1) & A(0) & A(3) & A(2);

when "11" \Rightarrow Z \Leftarrow A(0) & A(3 downto 1);

end case;

end process;

end uno;

```

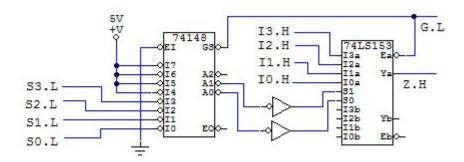

Página 3\_1. Diseñar un multiplexor de 16 entradas utilizando 4 multiplexores triestado de 4 entradas con habilitador (el circuito deshabilitado queda en alta impedancia) y un decodificador 2 a 4.

Indicar como debería diseñarse el circuito con dos chips 74'153, un chip 74'139 y una puerta lógica.

Un multiplexor de 16 entradas tiene, una salida Z, 16 entradas de datos I15-I0 seleccionadas por cuatro entradas de selección S3-S0, y puede tener una entrada de habilitación. Para construir un multiplexor de 16 entradas este circuito se necesitan al menos 4 multiplexores. Hay una

versión con cinco multiplexores de 4 entradas en la diapositiva 8 de teoría. Por el enunciado disponemos de cuatro multiplexores de 4 entradas y un decodificador 2 a 4. El método para diseñar el circuito consiste en conectar las salidas del decodificador a las entradas de habilitación de los multiplexores. De esta forma solo habrá cada vez un multiplexor habilitado y el resto deshabilitados. Lo más sencillo es conectar las entradas de selección más significativas a las entradas del decodificador y las menos significativas como entradas de selección de los multiplexores. Como hay cuatro salidas intermedias de cada uno de los multiplexores, y hay que juntarlas finalmente en una única salida, se necesita utilizar lógica adicional. Esta lógica depende de cómo funciona la deshabilitación de los multiplexores: si los deja en alta impedancia, como en el problema inicial, se podrían conectar todas las entradas juntas (en modo *wire*), si los deja a 0 como el 74'153 habría que usar una OR (X + 0 = X), si los deja a 1 habría que usar una AND ( $X \bullet 1 = X$ ).

El control de los multiplexores queda según esta tabla:

| <b>S3</b> | <b>S2</b> | MUX1 | MUX2 | MUX3 | MUX4 | Z (F(S1,S0))    |

|-----------|-----------|------|------|------|------|-----------------|

| 0         | 0         | ON   | OFF  | OFF  | OFF  | I3,I2,I1,I0     |

| 0         | 1         | OFF  | ON   | OFF  | OFF  | I7,I6,I5,I4     |

| 1         | 0         | OFF  | OFF  | ON   | OFF  | I11,I10,I9,I8   |

| 1         | 1         | OFF  | OFF  | OFF  | ON   | I15,I14,I13,I12 |

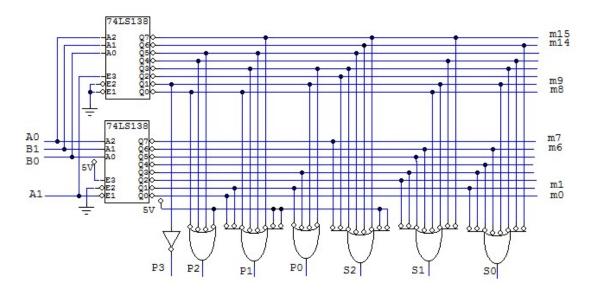

Los circuitos quedarían así:

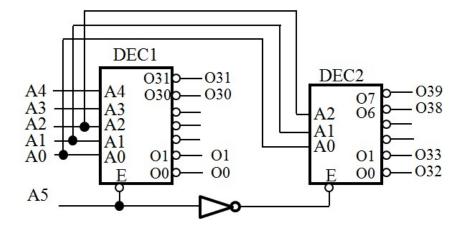

Página 3\_2. Se quiere diseñar un decodificador de 40 direcciones de 0 a 39 utilizando decodificadores binarios (2 a 4, 3 a 8, 4 a 16, etc). Indicar cuál es el número mínimo de decodificadores binarios que hay que utilizar y realizar el diseño del decodificador utilizando los decodificadores binarios y las puertas lógicas que sean necesarias (un inversor).

Hay que conseguir un decodificador con 40 direcciones usando el menor número de decodificadores binarios ideales. El circuito debe tener 6 entradas de direcciones (A5-A0) y 40 salidas. Como 42 = 32 + 8, se puede formar el circuito con dos decodificadores uno 5 a 32 (5 entradas de direcciones A4-A0), y otro de 3 a 8 (3 entradas de direcciones A2-A0). Elijo el decodificador DEC1 de 5 a 32 para las 32 direcciones más bajas (de 0 a 31), y el decodificador DEC2 3 a 8 para las direcciones más altas (de 32 a 39 que son de 0 a 7 en DEC2). Para seleccionar entre DEC1 y DEC2 necesito un decodificador de 1 a 2, pero ese decodificador lo puedo hacer únicamente con un inversor. El decodificador 1 a 2, debe tener como bit de dirección A5, y sus salidas deben ir conectadas a los habilitadores de DEC1 (O0) y DEC2 (O1). Cuando A5 es 0 DEC1 está habilitado y DEC2 está deshabilitado (salidas 32 a 39 a 0), en función de A4-A0 activo una de sus salidas 0-31, mientras que el resto de las salidas están a 0. Cuando A5 es 1 DEC1 está deshabilitado (salidas 0 a 31 a 0) y DEC2 está habilitado y activo una de sus 8 salidas según el valor de A2-A0. Algunos ejemplos de la operación:

| 32 | 16 | 8  | 4  | 2  | 1  |      |      |                    |                    |

|----|----|----|----|----|----|------|------|--------------------|--------------------|

| A5 | A4 | A3 | A2 | A1 | A0 | DEC1 | DEC2 | O31-0              | O39-32             |

| 0  | 0  | 0  | 0  | 0  | 0  | ON   | OFF  | O0 a 1, resto a 0  | salidas a 0        |

| 0  | 0  | 0  | 1  | 1  | 0  | ON   | OFF  | O6 a 1, resto a 0  | salidas a 0        |

| 0  | 1  | 0  | 1  | 0  | 0  | ON   | OFF  | O20 a 1, resto a 0 | salidas a 0        |

| 0  | 1  | 1  | 1  | 1  | 1  | ON   | OFF  | O31 a 1, resto a 0 | salidas a 0        |

| 1  | X  | X  | 0  | 0  | 0  | OFF  | ON   | salidas a 0        | O32 a 1, resto a 0 |

| 1  | X  | X  | 0  | 1  | 1  | OFF  | ON   | salidas a 0        | O35 a 1, resto a 0 |

| 1  | X  | X  | 1  | 1  | 1  | OFF  | ON   | salidas a 0        | O39 a 1, resto a 0 |

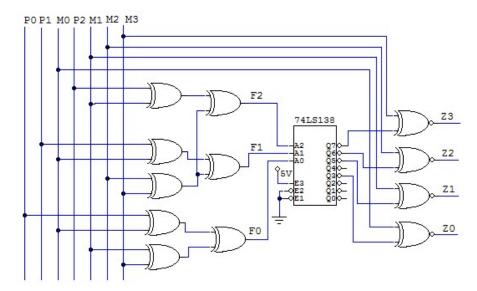

Página 3\_3. Diseñar un circuito decodificador del código de Hamming capaz de recuperar un error simple en un código (M0M1M2M3) con bits de paridad (P0P1P2) par utilizando puertas EXOR (para determinar F2F1F0 la dirección del bit erróneo, y para complementar dicho bit) y un 3 a 8 DEC (para indicar el bit erróneo en función de F2F1F0).

Para resolver este circuito usaré tres pasos. El primero genera los valores de (F2F1F0) en función de los bits de entrada. Cualquiera de las salidas F debe ser 1 cuando el número de bits de entrada a 1 es impar. Aunque la función lógica y el circuito asociado que realiza esto podría calcularse explícitamente con tablas de verdad y mapas de Karnaugh por ejemplo, se ha indicado en el tema IIa que una puerta EXOR puede considerarse como un circuito que calcula la paridad impar de las salidas (salida a 1 si el número de 1s en las entradas es impar), y hemos visto ejemplo de esto en una puerta EXOR de dos entradas o en la salida de suma de un "fulladder" de 1 bit (EXOR de 3 entradas). Según esto:

$$F2 = P2 \oplus M1 \oplus M2 \oplus M3$$

$F1 = P1 \oplus M0 \oplus M2 \oplus M3$

$F0 = P0 \oplus M0 \oplus M1 \oplus M3$

El segundo paso calcula el bit incorrecto. Una posibilidad es usar un decodificador 3 a 8. Las entradas de dirección son F2, F1 y F0. Si toman el valor binario 0 (000) no hay error, si toman un valor distinto la salida correspondiente del decodificador se fija a 1 y el resto de las salidas se fija a 0.

El tercer paso es utilizar un circuito entre la salida del codificador y la entrada correspondiente a su valor decimal. Si la salida del decodificador Oi es 0 (sin error), la entrada Ii debe mantenerse, y si es 1 (con error), la entrada debe complementarse. Este circuito ha aparecido en problemas anteriores (tema IIa), y corresponde a una EXOR, como se ve en la tabla.

| Oi | Ii | Zi |

|----|----|----|

| 0  | 0  | 0  |

| 0  | 1  | 1  |

| 1  | 0  | 1  |

| 1  | 1  | 0  |

Como solo hace falta obtener los bits de datos M0, M1, M2 y M3:

$$Z0 = O3 \bigoplus M0$$

$Z1 = O5 \bigoplus M1$

$Z2 = O6 \bigoplus M2$

$Z3 = O7 \bigoplus M3$

Si las salidas del decodificador están en lógica negativa, como en los circuitos comerciales de la familia 74, la operación cambia y se debería implementar con puertas EXNOR.

$$Z0 = \overline{03 \oplus M0} = O3 \oplus M0$$

$$Z1 = \overline{05 \oplus M1} = O5 \oplus M1$$

$$Z2 = \overline{06 \oplus M2} = O6 \oplus M2$$

$$Z3 = \overline{07 \oplus M3} = O7 \oplus M3$$

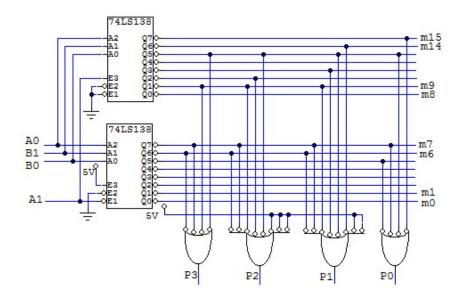

Página 4\_1. Realizar un multiplicador para números A (a1a0) y B (b1b0) de 2 bits en complemento-2, utilizando decodificadores 74LS138 y puertas NAND de 4 entradas (74LS20) o de 8 entradas (74LS30). El resultado P (p3p2p1p0) es de 4 bits en complemento-2.

Estos circuitos se desarrollan a partir de la tabla de verdad del problema y se implementan como si fuese una ROM, pero en vez de usar un plano OR programable, hago las líneas OR con puertas lógicas. Como las salidas del decodificador están en lógica negativa las entradas de las puertas OR también deben estarlo, lo que implica que se usan puertas NAND.

|    |    | -2        | 1  | -2 | 1         |     |    | -8 | 4  | 2  | 1  |

|----|----|-----------|----|----|-----------|-----|----|----|----|----|----|

| A  | В  | <b>A1</b> | A0 | B1 | <b>B0</b> | DEC | P  | P3 | P2 | P1 | P0 |

| 0  | 0  | 0         | 0  | 0  | 0         | 0   | 0  | 0  | 0  | 0  | 0  |

| 0  | 1  | 0         | 0  | 0  | 1         | 1   | 0  | 0  | 0  | 0  | 0  |

| 0  | -2 | 0         | 0  | 1  | 0         | 2   | 0  | 0  | 0  | 0  | 0  |

| 0  | -1 | 0         | 0  | 1  | 1         | 3   | 0  | 0  | 0  | 0  | 0  |

| 1  | 0  | 0         | 1  | 0  | 0         | 4   | 0  | 0  | 0  | 0  | 0  |

| 1  | 1  | 0         | 1  | 0  | 1         | 5   | 1  | 0  | 0  | 0  | 1  |

| 1  | -2 | 0         | 1  | 1  | 0         | 6   | -2 | 1  | 1  | 1  | 0  |

| 1  | -1 | 0         | 1  | 1  | 1         | 7   | -1 | 1  | 1  | 1  | 1  |

| -2 | 0  | 1         | 0  | 0  | 0         | 8   | 0  | 0  | 0  | 0  | 0  |

| -2 | 1  | 1         | 0  | 0  | 1         | 9   | -2 | 1  | 1  | 1  | 0  |

| -2 | -2 | 1         | 0  | 1  | 0         | 10  | 4  | 0  | 1  | 0  | 0  |

| -2 | -1 | 1         | 0  | 1  | 1         | 11  | 2  | 0  | 0  | 1  | 0  |

| -1 | 0  | 1         | 1  | 0  | 0         | 12  | 0  | 0  | 0  | 0  | 0  |

| -1 | 1  | 1         | 1  | 0  | 1         | 13  | -1 | 1  | 1  | 1  | 1  |

| -1 | -2 | 1         | 1  | 1  | 0         | 14  | 2  | 0  | 0  | 1  | 0  |

| -1 | -1 | 1         | 1  | 1  | 1         | 15  | 1  | 0  | 0  | 0  | 1  |

Según esta tabla:

P3 = F3 (A1, A0, B1, B0) =

$$\sum$$

(6, 7, 9, 13)

P2 = F2 (A1, A0, B1, B0) =  $\sum$  (6, 7, 9, 10, 13)

P1 = F1 (A1, A0, B1, B0) =  $\sum$  (6, 7, 9, 11, 13, 14)

P0 = F0 (A1, A0, B1, B0) =  $\sum$  (5, 7, 13, 15)

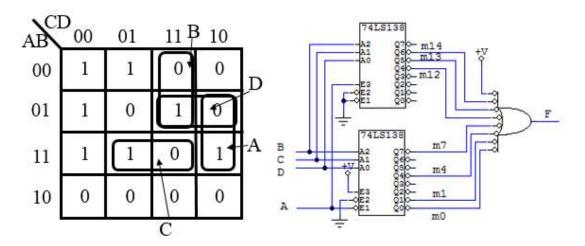

Como el problema tiene 4 entradas, la implementación debe hacerse con un decodificador de 4 a 16. El enunciado del problema pide que el circuito a usar sea un 74'138, que es un decodificador 3 a 8, por lo que hay usar dos en la configuración de la diapositiva 15 de teoría. Para las salidas P3 y P2 se pueden usar puertas NAND de 4 entradas, pero para las salidas P2 y P1 se necesitan puertas NAND de 8 entradas; las entradas no usadas se conectan a alto. El circuito queda así:

Página 4\_2. Diseñar un circuito que realice simultáneamente:

- a) La suma de dos números positivos X (X1.H, X0.H) e Y (Y1.H Y0.H) de dos bits.

- b) El producto de dos números positivos M (M1.H, M0.L) e N (N1.L N0.H) de dos bits.

El circuito debe tener solo cuatro bits de entrada y dos grupos diferenciados de salidas para cada una de las operaciones, todas las salidas deben ser de polaridad positiva. El diseño debe realizarse utilizando el menor número de decodificadores 74'138, y el menor número de puertas NAND (suponer que es posible cualquier número de entradas en las puertas).

Este problema es similar al anterior. Hay dos entradas de dos bits, que llamamos A (A1, A0) y (B1, B0), con valores entre 0 y 3, que se comportan como X e Y para hacer la suma, y como M y N para hacer la multiplicación. La suma S de operando de dos bits nos da un resultado de 3 bits (S2, S1, S0, 3+3 = 6), y el producto de operando de dos bits da un resultado de 4 bits (P3, P2, P1, P0, 3\*3 = 9). En total son 7 salidas. En principio, como en el problema anterior, el problema puede resolverse con dos decodificadores 74'138 y 7 puertas NAND.

Hay un problema adicional en el producto, ya que en este caso las entradas M0 (A0) y N1 (B1) están en lógica negativa. Para utilizar el mismo circuito hay que suponer que en el producto A0 es  $\overline{\text{M0}}$  y B1 es  $\overline{\text{N1}}$ , con lo que cambian la posición de los *minterms*, es decir si M = N = 0 (00) y el producto P es 0 (0000), entonces A es 1 (01) y B es 2 (10), con lo que en notación decimal (A1A0B1B0) es 6 (01 10). Las tablas se pueden desarrollar para la suma y el producto. En las tablas aparecen los valores numéricos de X (X1, X0) e Y (Y1, Y0), y M (M1, M0) y N (N1, N0), en decimal y en binario, el resultado de la operación para los valores de X e Y, o M y N en decimal (S, P) y binario (S2S1S0, P3P2P1P0), y cómo X e Y, o M y N se convierten en A y B en binario (A1A0B1B0), y la notación decimal para la suma (DECS) o el producto (DECP), que se toma como base para obtener la función lógica de cada una de las salidas.

|   |   | 2  | 1  | 2         | 1  |   | 4         | 2  | 1  | 8         | 4  | 2  | 1         | _    |

|---|---|----|----|-----------|----|---|-----------|----|----|-----------|----|----|-----------|------|

| X | Y | X1 | X0 | <b>Y1</b> | Y0 | S | <b>S2</b> | S1 | S0 | <b>A1</b> | A0 | B1 | <b>B0</b> | DECS |

| 0 | 0 | 0  | 0  | 0         | 0  | 0 | 0         | 0  | 0  | 0         | 0  | 0  | 0         | 0    |

| 0 | 1 | 0  | 0  | 0         | 1  | 1 | 0         | 0  | 1  | 0         | 0  | 0  | 1         | 1    |

| 0 | 2 | 0  | 0  | 1         | 0  | 2 | 0         | 1  | 0  | 0         | 0  | 1  | 0         | 2    |

| 0 | 3 | 0  | 0  | 1         | 1  | 3 | 0         | 1  | 1  | 0         | 0  | 1  | 1         | 3    |

| 1 | 0 | 0  | 1  | 0         | 0  | 1 | 0         | 0  | 1  | 0         | 1  | 0  | 0         | 4    |

| 1 | 1 | 0  | 1  | 0         | 1  | 2 | 0         | 1  | 0  | 0         | 1  | 0  | 1         | 5    |

| 1 | 2 | 0  | 1  | 1         | 0  | 3 | 0         | 1  | 1  | 0         | 1  | 1  | 0         | 6    |

| 1 | 3 | 0  | 1  | 1         | 1  | 4 | 1         | 0  | 0  | 0         | 1  | 1  | 1         | 7    |

| 2 | 0 | 1  | 0  | 0         | 0  | 2 | 0         | 1  | 0  | 1         | 0  | 0  | 0         | 8    |

| 2 | 1 | 1  | 0  | 0         | 1  | 3 | 0         | 1  | 1  | 1         | 0  | 0  | 1         | 9    |

| 2 | 2 | 1  | 0  | 1         | 0  | 4 | 1         | 0  | 0  | 1         | 0  | 1  | 0         | 10   |

| 2 | 3 | 1  | 0  | 1         | 1  | 5 | 1         | 0  | 1  | 1         | 0  | 1  | 1         | 11   |

| 3 | 0 | 1  | 1  | 0         | 0  | 3 | 0         | 1  | 1  | 1         | 1  | 0  | 0         | 12   |

| 3 | 1 | 1  | 1  | 0         | 1  | 4 | 1         | 0  | 0  | 1         | 1  | 0  | 1         | 13   |

| 3 | 2 | 1  | 1  | 1         | 0  | 5 | 1         | 0  | 1  | 1         | 1  | 1  | 0         | 14   |

| 3 | 3 | 1  | 1  | 1         | 1  | 6 | 1         | 1  | 0  | 1         | 1  | 1  | 1         | 15   |

$$S2 = F2(A1, A0, B1, B0) = \sum(7, 10, 11, 13, 14, 15)$$

$$S1 = F1(A1, A0, B1, B0) = \sum(2, 3, 5, 6, 8, 9, 12, 15)$$

$$S0 = F0(A1, A0, B1, B0) = \sum(1, 3, 4, 6, 9, 11, 12, 14)$$

|   |   | 2  | 1  | 2  | 1  |   | 8  | 4  | 2  | 1  | 8  | 4  | 2  | 1         |      |

|---|---|----|----|----|----|---|----|----|----|----|----|----|----|-----------|------|

| M | N | M1 | M0 | N1 | N0 | P | P3 | P2 | P1 | P0 | A1 | A0 | B1 | <b>B0</b> | DECP |

| 0 | 0 | 0  | 0  | 0  | 0  | 0 | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0         | 6    |

| 0 | 1 | 0  | 0  | 0  | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1         | 7    |

| 0 | 2 | 0  | 0  | 1  | 0  | 0 | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0         | 4    |

| 0 | 3 | 0  | 0  | 1  | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1         | 5    |

| 1 | 0 | 0  | 1  | 0  | 0  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0         | 2    |

| 1 | 1 | 0  | 1  | 0  | 1  | 1 | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1         | 3    |

| 1 | 2 | 0  | 1  | 1  | 0  | 2 | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0         | 0    |

| 1 | 3 | 0  | 1  | 1  | 1  | 3 | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 1         | 1    |

| 2 | 0 | 1  | 0  | 0  | 0  | 0 | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0         | 14   |

| 2 | 1 | 1  | 0  | 0  | 1  | 2 | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 1         | 15   |

| 2 | 2 | 1  | 0  | 1  | 0  | 4 | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 0         | 12   |

| 2 | 3 | 1  | 0  | 1  | 1  | 6 | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1         | 13   |

| 3 | 0 | 1  | 1  | 0  | 0  | 0 | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0         | 10   |

| 3 | 1 | 1  | 1  | 0  | 1  | 3 | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 1         | 11   |

| 3 | 2 | 1  | 1  | 1  | 0  | 6 | 0  | 1  | 1  | 0  | 1  | 0  | 0  | 0         | 8    |

| 3 | 3 | 1  | 1  | 1  | 1  | 9 | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1         | 9    |

```

P3 = F7(A1, A0, B1, B0) = \sum(9)

```

$P2 = F6(A1, A0, B1, B0) = \overline{\sum}(8, 12, 13)$

$P1 = F5(A1, A0, B1, B0) = \sum_{i=0}^{\infty} (0, 1, 8, 11, 13, 15)$

$P0 = F4(A1, A0, B1, B0) = \sum_{i=1}^{n} (1, 3, 9, 11)$

Implemento usando decodificadores y puertas NAND. Aunque, según el enunciado, puedo usar puertas NAND con cualquier número de entradas, en el diseño uso un inversor para P3, y puertas de 4 y 8 entradas conectando las entradas no usadas a 1 lógico.

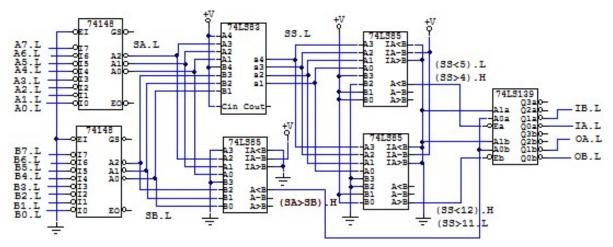

Página 5\_1. Implementar las siguientes funciones utilizando el menor número de decodificadores 3 a 8, y 2 a 4.

## a) $F(A,B,C,D) = \sum (0,1,4,7,12,13,14) \text{ con A.H, B.H, C.H y D.H.}$

Primero compruebo si hay alguna entrada es redundante. Utilizo el método usado con los multiplexores (diapositivas 25 y 26 de teoría), basado en el mapa de Karnaugh (buscar un 1-cubo con valores 0-1 para cada entrada). No hay entradas redundantes, y como todas las entradas están en lógica positiva implemento directamente con los decodificadores 3 a 8 74'138 y una puerta NAND.

Otra opción posible realiza la implementación usando únicamente decodificadores 2 a 4 como en la diapositiva 16 de teoría. En el mapa se ve que hay 2-cubos de 0s (A $\overline{B}$ , por ejemplo) y no hay 2-cubos de 1s. Conectando A a A3, B a A2, C a A1 y D a A0, habría que conectar las salidas del decodificador O0, O1, O4, O7, O12, O13 y O14 a las entradas de una puerta NAND como en la figura anterior. Como no se usan ninguna de las salidas O<sub>8-11</sub>, el decodificador correspondiente es innecesario y se puede eliminar del diseño. Queda propuesto.

## b) $F(A,B,C,D,E) = \sum (0,2,4,5,7,8,9,10,13,17,26,27)$ con A.H, B.L, C.L, D.L y E.H.

Es un circuito de 5 entradas por lo que, en principio, se necesita un decodificador de 5 a 32. Lo primero es usar un mapa de Karnaugh para comprobar si alguna entrada es redundante. Los 1-cubos para la entrada A son la misma casilla de los dos mapas de 4 entradas.

| BC   | E 00 F | 01_ | 11  | 10 | A BC     | E 00_ | .01 | 11  | 10 |

|------|--------|-----|-----|----|----------|-------|-----|-----|----|

| 00   | 1      | 0   | 0   | 1  | 00       | 0     | 1   | 0   | 0  |

| 01   | 1      | 1   | 1   | 0  | –С<br>01 | 0     | 0   | 0   | 0  |

| B 11 | 0      | 1   | Q   | 9  | -D 11    | 0     | 0   | 0   | 0  |

| 10   | 1      | 1   | 1   | 0  | 10       | 0     | 0   | 1   | 1  |

|      |        | Α=  | = 0 |    |          | 6     | Α=  | : 1 | 35 |

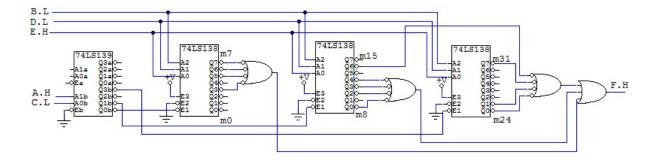

Del mapa de Karnaugh se observa que no hay entradas redundantes. Lo más lógico es hacer una implementación de los decodificadores con dos niveles. El primero es un decodificador 2 a 4 con dos bits de dirección (normalmente A y B), y el segundo cuatro decodificadores 3 a 8, los cuatro con los mismos tres bits de dirección (normalmente C, D y E).

Pero además se observa en el mapa que hay solo un 3-cubo de 0s con (AC) = (11). Eso significa que si reordeno las entradas como (AC) para el decodificador 2 a 4 y (BDE) para los decodificadores 3 a 8, puedo eliminar uno de los 4 decodificadores 3 a 8. Por último, las entradas B, C y D son .L, por lo que se complementan los 1s y 0s para saber los *minterms* que hay que utilizar. Por lo que uso:

$$F(A, C, B, D, E) = \sum (3, 5, 6, 7, 8, 10, 11, 12, 14, 24, 25, 31)$$

|     | 16 | 8 | 4 | 2 | 1 | 16 | 8 | 4 | 2 | 1 |     |

|-----|----|---|---|---|---|----|---|---|---|---|-----|

| DEC | A  | В | C | D | E | A  | C | В | D | E | DEC |

| 0   | 0  | 0 | 0 | 0 | 0 | 0  | 1 | 1 | 1 | 0 | 14  |

| 2   | 0  | 0 | 0 | 1 | 0 | 0  | 1 | 1 | 0 | 0 | 12  |

| 4   | 0  | 0 | 1 | 0 | 0 | 0  | 0 | 1 | 1 | 0 | 6   |

| 5   | 0  | 0 | 1 | 0 | 1 | 0  | 0 | 1 | 1 | 1 | 7   |

| 7   | 0  | 0 | 1 | 1 | 1 | 0  | 0 | 1 | 0 | 1 | 5   |

| 8   | 0  | 1 | 0 | 0 | 0 | 0  | 1 | 0 | 1 | 0 | 10  |

| 9   | 0  | 1 | 0 | 0 | 1 | 0  | 1 | 0 | 1 | 1 | 11  |

| 10  | 0  | 1 | 0 | 1 | 0 | 0  | 1 | 0 | 0 | 0 | 8   |

| 13  | 0  | 1 | 1 | 0 | 1 | 0  | 0 | 0 | 1 | 1 | 3   |

| 17  | 1  | 0 | 0 | 0 | 1 | 1  | 1 | 1 | 1 | 1 | 31  |

| 26  | 1  | 1 | 0 | 1 | 0 | 1  | 1 | 0 | 0 | 0 | 24  |

| 27  | 1  | 1 | 0 | 1 | 1 | 1  | 1 | 0 | 0 | 1 | 25  |

Implemento el circuito con los 3 circuitos 74LS138 (DEC 3 a 8) y un circuito 74LS139 (DEC 2 a 4, uso solo uno de los dos decodificadores). En la diapositiva 15 de teoría se muestra cómo se podría sustituir el DEC 2 a 4 por un único inversor. Hago la OR final con 3 NANDs de 4 entradas y una OR de 3 entradas.

Página 5\_1. Implementar las siguientes funciones lógicas utilizando un único multiplexor, lo más pequeño posible.

a)

$$F(A,B,C,D) = \sum (0,1,4,7,12,13,14) + \sum_{\phi} (5,10,15) \text{ con A.H, B.H, C.H y D.H, F.H.}$$

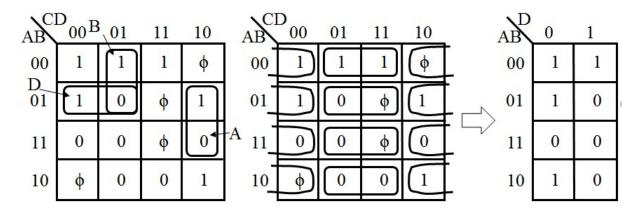

Primero compruebo si hay alguna entrada redundante con el mapa de Karnaugh. Como para todas las entradas se puede encontrar por lo menos un 1-cubo con 0 y 1, entonces todas las entradas son necesarias, y el problema es de 4 entradas.

| ABCI | D <sub>00</sub> | 01 | C 11 F | 3 10    |    |

|------|-----------------|----|--------|---------|----|

| 00   | 1               | 1  | O*     | 0       | D  |

| 01   | 1               | ф  | 1      | <u></u> |    |

| 11   | 1               | 1  | ф      | 1       | -A |

| 10   | 0               | 0  | 0      | ф       |    |

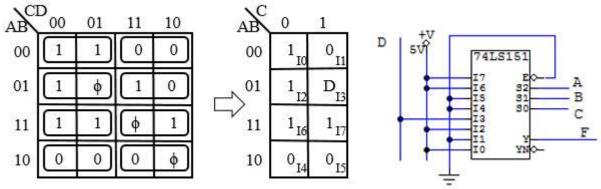

Voy a hacer una implementación de tipo 1, en la que elijo una entrada que aplico a las entradas de datos del multiplexor, y las otras tres entradas a las entradas de selección del multiplexor. Entonces se necesita un multiplexor de 8 entradas, y como máximo un inversor para las entradas de datos. Elijo la variable D aleatoriamente la introduzco en el mapa. Comparo en el mapa de Karnaugh el valor de la función con el valor de D en los márgenes y escribo 0, (dos 0s), 1 (dos 1s), D (valores iguales) o  $\overline{D}$  (valores complementarios).

Dentro de cada casilla aparece la entrada de datos del multiplexor a la que se tiene que conectar el valor. Como todas las entradas están en polaridad positiva no hay que hacer más operaciones y genero el circuito.

b)

$$F(A,B,C,D) = \sum (0, 1, 3, 4, 6, 10) + \sum_{\phi} (2, 7, 8, 15)$$

para A.L, B.H, C.H, D.L, F.H.

Repito el procedimiento para esta función. Compruebo si hay alguna entrada redundante. A, B y D no lo son, pero utilizando los "don't cares" y asignándole 0 o 1, según convenga, consigo que la función no dependa de C. Como ahora la función tiene tres entradas, y voy a aplicar una a las entradas de datos, hay que aplicar las otras dos a entradas de selección del multiplexor, por lo que necesito un multiplexor de 4 entradas.

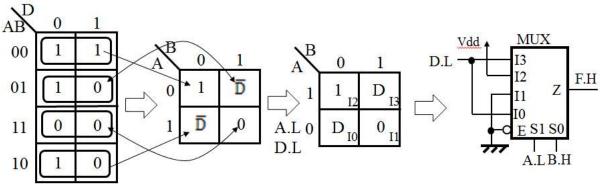

$$F(A,B,C,D) = \sum_{i=0}^{\infty} (0, 1, 3, 4, 6, 10) + \sum_{i=0}^{\infty} (2, 7, 8, 15) = F1(A,C,D) = \sum_{i=0}^{\infty} (0, 1, 2, 4)$$

Introduzco una entrada en el mapa. Elijo D. Ajusto la polaridad de las entradas, para lo que complemento las entradas .L: A en los márgenes del mapa, y D en las casillas del mapa. Como en las entradas de selección sitúo A (S1) y B (S0), el valor binario de las entradas (AB) indica el índice de las entradas de datos que se corresponde con cada casilla del mapa. Implemento en un multiplexor de 4 entradas conectando 0 a GND, 1 a la tensión de alimentación, D a la variable de entrada y  $\overline{D}$  al inversor de D.

Página 5\_3. Implementar utilizando un multiplexor de cuatro entradas y el menor número de multiplexores de dos entradas la función lógica: F.H = F(A,B,C,D) =  $\prod (1,5,9,11,12,13,14) \cdot \prod_{\phi} (7,15)$ , para entradas A.H, B.L, C.H y D.L.

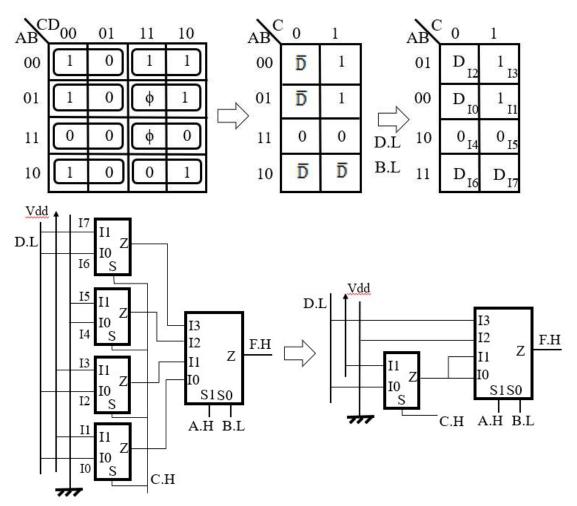

La función tiene cuatro entradas por lo que se necesita, en principio, un multiplexor de 8 entradas, que se puede construir con un multiplexor de 4 entradas y multiplexores de dos entradas, usando la configuración de la diapositiva 7 de teoría. Siguiendo los pasos compruebo si alguna entrada es redundante: no las hay.

| AB      | 000 | 01 | 11 | 10 | _  |

|---------|-----|----|----|----|----|

| 00<br>D | 1   | 0  | 1  | 1  |    |

| 01<br>B | 1   | 0  | ф  | 1  |    |

| 11      | 0   | 0  | ф  | 0  | -A |

| 10      | 1   | 0  | 0  | 1  |    |

El objetivo es encontrar una solución con el menor número de multiplexores de dos entradas. Para conseguir la solución mínima hay que hacer pruebas sobre qué entradas son de selección del multiplexor de 4 entradas, el valor lógico asociado a los "don't cares", etc. La solución es que no se necesita ninguno. De momento sigo el orden convencional e intento minimizar el número de multiplexores: A y B son las entradas de selección del multiplexor de 4 entradas, C de los de 2 entradas y D en las entradas de datos. Meto D en el mapa y ajusto su polaridad.

El circuito de la izquierda puede reducirse ya que los dos multiplexores inferiores de dos entradas son iguales por lo que se puede eliminar uno, y los otros multiplexores tienen las dos entradas conectadas iguales (0 y D.L), luego puede sustituirse por el valor de las entradas (0 y D.L). Tres multiplexores se pueden eliminar, produciendo el circuito de la derecha.

Para conseguir hacer un circuito sin multiplexores de dos entradas, hay que meter C en el mapa, suponiendo que el *minterm* 7 es 1 y el 15 es 0. Además, las entradas de selección del multiplexor de 4 entradas son A y D, y la de los multiplexores de 2 entradas es B. En la figura, después de meter C en el mapa y ajustar la polaridad ordeno las entradas I0-I7 en función de ADB, cada par de casillas marcadas es un multiplexor: I0-I1 es C y no requiere multiplexor; igualmente I2-I3 son 1, e I4-I5 son 0. Por último, en I6-I7, si B es 0, F es 0, y si B es 1, F es 1, por lo que F es igual a B, y tampoco necesitan multiplexor.

Página 6\_1. Obtener las expresiones lógicas minimizadas que permiten encontrar cuál de 7 líneas de entrada A1, A4, A6, A8, A9, A13, A14 está puesta a valor lógico 1, dando como resultado su correspondiente codificación binaria: por ejemplo, A8 daría como resultado 8 en la salida (codificado en binario).

- a) Solo puede estar una línea a valor lógico 1.

- b) Varias líneas de entrada están simultáneamente a 1, pero la salida tomará el valor binario de la línea de índice más bajo.

- a) La descripción del circuito corresponde a un codificador sin prioridad, que se puede implementar con puertas OR. La salida máxima es 14, que se requiere 4 bits de salida Z3, Z2, Z1 y Z0.

| A1 | A4 | <b>A6</b> | A8 | A9 | A13 | A14 | <b>Z</b> 3 | <b>Z2</b> | <b>Z</b> 1 | <b>Z</b> 0 |

|----|----|-----------|----|----|-----|-----|------------|-----------|------------|------------|

| 1  | 0  | 0         | 0  | 0  | 0   | 0   | 0          | 0         | 0          | 1          |

| 0  | 1  | 0         | 0  | 0  | 0   | 0   | 0          | 1         | 0          | 0          |

| 0  | 0  | 1         | 0  | 0  | 0   | 0   | 0          | 1         | 1          | 0          |

| 0  | 0  | 0         | 1  | 0  | 0   | 0   | 1          | 0         | 0          | 0          |

| 0  | 0  | 0         | 0  | 1  | 0   | 0   | 1          | 0         | 0          | 1          |

| 0  | 0  | 0         | 0  | 0  | 1   | 0   | 1          | 1         | 0          | 1          |

| 0  | 0  | 0         | 0  | 0  | 0   | 1   | 1          | 1         | 1          | 0          |

$$Z3 = A8 + A9 + A13 + A14$$

$$Z2 = A4 + A6 + A13 + A14$$

$$Z1 = A6 + A14$$

$$Z0 = A1 + A9 + A13$$

b) La descripción ahora corresponde a un codificador con prioridad baja. La tabla de este problema quedaría así:

| Función                                                                                               | A1 | A4 | <b>A6</b> | A8 | A9 | A13 | A14 | <b>Z</b> 3 | <b>Z2</b> | <b>Z</b> 1 | <b>Z</b> 0 |

|-------------------------------------------------------------------------------------------------------|----|----|-----------|----|----|-----|-----|------------|-----------|------------|------------|

| A1                                                                                                    | 1  | X  | X         | X  | X  | X   | X   | 0          | 0         | 0          | 1          |

| <u>A1</u> A4                                                                                          | 0  | 1  | X         | X  | X  | X   | X   | 0          | 1         | 0          | 0          |

| $\overline{A1} \overline{A4} A6$                                                                      | 0  | 0  | 1         | X  | X  | X   | X   | 0          | 1         | 1          | 0          |

| $\overline{A1} \overline{A4} \overline{A6} A8$                                                        | 0  | 0  | 0         | 1  | X  | X   | X   | 1          | 0         | 0          | 0          |

| $\overline{A1} \overline{A4} \overline{A6} \overline{A8} A9$                                          | 0  | 0  | 0         | 0  | 1  | X   | X   | 1          | 0         | 0          | 1          |

| $\overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} A13$                           | 0  | 0  | 0         | 0  | 0  | 1   | X   | 1          | 1         | 0          | 1          |

| $\overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} \overline{A13} A14$            | 0  | 0  | 0         | 0  | 0  | 0   | 1   | 1          | 1         | 1          | 0          |

| $\overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} \overline{A13} \overline{A14}$ | 0  | 0  | 0         | 0  | 0  | 0   | 0   | 0          | 0         | 0          | 0          |

$Z3 = \overline{A1} \overline{A4} \overline{A6} \overline{A8} + \overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} + \overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} \overline{A13} + \overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} \overline{A13} \overline{A14}$

$Z2 = \overline{A1} \ A4 + \overline{A1} \ \overline{A4} \ A6 + \overline{A1} \ \overline{A4} \ \overline{A6} \ \overline{A8} \ \overline{A9} \ A13 + \overline{A1} \ \overline{A4} \ \overline{A6} \ \overline{A8} \ \overline{A9} \ \overline{A13} \ A14$

$Z1 = \overline{A1} \overline{A4} A6 + \overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} \overline{A13} A14$

$= A1 + \overline{A4} \overline{A6} \overline{A8} (A9 + A13)$

$Z0 = A1 + \overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} + \overline{A1} \overline{A4} \overline{A6} \overline{A8} \overline{A9} \overline{A13}$

Las ecuaciones se pueden reducir con la propiedad distributiva y el teorema de simplificación  $(X + \overline{X}Y = X + Y)$ .

```

Z3 = \overline{A1} \, \overline{A4} \, \overline{A6} \, (A8 + \overline{A8} \, A9 + \overline{A8} \, \overline{A9} \, A13 + \overline{A8} \, \overline{A9} \, \overline{A13} \, A14 \,) =

= \overline{A1} \, \overline{A4} \, \overline{A6} \, (A8 + A9 + \overline{A9} \, A13 + \overline{A9} \, \overline{A13} \, A14 \,) =

= \overline{A1} \, \overline{A4} \, \overline{A6} \, (A8 + A9 + A13 + \overline{A13} \, A14) = \overline{A1} \, \overline{A4} \, \overline{A6} \, (A8 + A9 + A13 + A14)

Z2 = \overline{A1} \, (A4 + \overline{A4} \, A6 + \overline{A4} \, \overline{A6} \, \overline{A8} \, \overline{A9} \, A13 + \overline{A4} \, \overline{A6} \, \overline{A8} \, \overline{A9} \, \overline{A13} \, A14) =

= \overline{A1} \, (A4 + A6 + \overline{A6} \, \overline{A8} \, \overline{A9} \, A13 + \overline{A6} \, \overline{A8} \, \overline{A9} \, \overline{A13} \, A14) =

= \overline{A1} \, (A4 + A6 + \overline{A8} \, \overline{A9} \, A13 + \overline{A8} \, \overline{A9} \, \overline{A13} \, A14) =

= \overline{A1} \, [A4 + A6 + \overline{A8} \, \overline{A9} \, (A13 + \overline{A13} \, A14)] = \overline{A1} \, [A4 + A6 + \overline{A8} \, \overline{A9} \, (A13 + A14)]

Z1 = \overline{A1} \, \overline{A4} \, (A6 + \overline{A6} \, \overline{A8} \, \overline{A9} \, \overline{A13} \, A14) = \overline{A1} \, \overline{A4} \, (A6 + \overline{A8} \, \overline{A9} \, \overline{A13} \, A14)

Z0 = A1 + \overline{A4} \, \overline{A6} \, \overline{A8} \, A9 + \overline{A4} \, \overline{A6} \, \overline{A8} \, \overline{A9} \, A13 = A1 + \overline{A4} \, \overline{A6} \, \overline{A8} \, (A9 + \overline{A9} \, A13) =

```

Página 6\_2. Encontrar las ecuaciones lógicas que permiten definir un circuito codificador con prioridad baja de 8 bits de entrada (I7-I0) y salidas en código Gray (de más a menos significativas: A B C).

Para el problema del enunciado, su tabla de verdad queda como se muestra. Los valores de las salidas cuando ninguna entrada está activa (0s) podrían definirse de otra manera.

| Función                  | 10 | <b>I1</b> | <b>I2</b> | <b>I3</b> | <b>I4</b> | <b>I5</b> | <b>I6</b> | <b>I7</b> | A | В | C |

|--------------------------|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---|---|---|

| I0                       | 1  | X         | X         | X         | X         | X         | X         | X         | 0 | 0 | 0 |

| <u>10</u> 11             | 0  | 1         | X         | X         | X         | X         | X         | X         | 0 | 0 | 1 |

| <u>10</u> 11 12          | 0  | 0         | 1         | X         | X         | X         | X         | X         | 0 | 1 | 1 |

| <u>10 11 12 13</u>       | 0  | 0         | 0         | 1         | X         | X         | X         | X         | 0 | 1 | 0 |

| <u>10 11 12 13 14</u>    | 0  | 0         | 0         | 0         | 1         | X         | X         | X         | 1 | 1 | 0 |

| <u>10 11 12 13 14 15</u> | 0  | 0         | 0         | 0         | 0         | 1         | X         | X         | 1 | 1 | 1 |

| ĪŪ ĪĪ ĪZ ĪЗ Ī4 Ī5 I6     | 0  | 0         | 0         | 0         | 0         | 0         | 1         | X         | 1 | 0 | 1 |

| <u> </u>                 | 0  | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 1 | 0 | 0 |

| <u> </u>                 | 0  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0 | 0 | 0 |

```

A = \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ 14 + \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ \overline{14} \ 15 + \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ \overline{14} \ \overline{15} \ 16 + \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ \overline{14} \ \overline{15} \ \overline{16} \ 17

B = \overline{10} \ \overline{11} \ 12 + \overline{10} \ \overline{11} \ \overline{12} \ 13 + \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ 14 + \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ \overline{14} \ 15

```

$C = \overline{10} \text{ } \overline{11} + \overline{10} \overline{11} \overline{12} + \overline{10} \overline{11} \overline{12} \overline{13} \overline{14} \overline{15} + \overline{10} \overline{11} \overline{12} \overline{13} \overline{14} \overline{15} \overline{16}$

Al igual que en el problema anterior uso la propiedad distributiva y el teorema de simplificación para reducir las expresiones lógicas:

```

A = \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ (14 + \overline{14} \ 15 + \overline{14} \ \overline{15} \ 16 + \overline{14} \ \overline{15} \ \overline{16} \ 17) = \\ = \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ (14 + 15 + 15 \ 16 + \overline{15} \ \overline{16} \ 17) = \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ (14 + 15 + 16 + \overline{16} \ 17) = \\ = \overline{10} \ \overline{11} \ \overline{12} \ \overline{13} \ (14 + 15 + 16 + 17)

B = \overline{10} \ \overline{11} \ (12 + \overline{12} \ 13 + \overline{12} \ \overline{13} \ 14 + \overline{12} \ \overline{13} \ \overline{14} \ 15) = \overline{10} \ \overline{11} \ (12 + 13 + \overline{13} \ 14 + \overline{13} \ \overline{14} \ 15) = \\ = \overline{10} \ \overline{11} \ (12 + 13 + 14 + \overline{14} \ 15) = \overline{10} \ \overline{11} \ (12 + 13 + 14 + 15)

C = \overline{10} \ (11 + \overline{11} \ 12 + \overline{11} \ \overline{12} \ \overline{13} \ \overline{14} \ 15 + \overline{11} \ \overline{12} \ \overline{13} \ \overline{14} \ \overline{15} \ 16) = \\ = \overline{10} \ (11 + 12 + \overline{12} \ \overline{13} \ \overline{14} \ 15 + \overline{15} \ 16) = \overline{10} \ [11 + 12 + \overline{13} \ \overline{14} \ (15 + \overline{16})]

```

Página 6\_3. Construir un circuito codificador binario de 8 a 3 con prioridad baja tomando como base el circuito codificador 74LS148, y el menor número posible de puertas lógicas que sean necesarias. Se permite definir como mejor convenga la polaridad de las entradas y de las salidas.

La tabla del funcionamiento del circuito 74LS148 aparece en la diapositiva 34 de teoría. Por defecto las entradas y salidas están en lógica negativa, y la prioridad de las entradas es alta: I7 a 1, genera L L L en las salidas A2 A1 A0, que es (111)<sub>2</sub> en lógica negativa, o (7)<sub>10</sub>.

|    |   |   | IN | PUT | S |   |   |   | OUTPUTS |    |    |    |    |  |  |

|----|---|---|----|-----|---|---|---|---|---------|----|----|----|----|--|--|

| ΕI | 0 | 1 | 2  | 3   | 4 | 5 | 6 | 7 | A2      | A1 | A0 | GS | EO |  |  |

| Н  | × | × | ×  | ×   | × | × | × | × | н       | н  | н  | н  | н  |  |  |

| L  | н | н | н  | н   | н | н | н | н | H       | H  | н  | н  | L  |  |  |

| L  | × | × | ×  | ×   | × | × | × | L | L       | L  | L  | L  | н  |  |  |

| L  | × | × | ×  | ×   | × | × | L | н | L       | L  | н  | L  | н  |  |  |

| L  | × | × | ×  | ×   | X | L | н | н | L       | н  | L  | L  | н  |  |  |

| L  | × | × | ×  | ×   | L | н | н | н | L       | н  | н  | L  | н  |  |  |

| L  | × | × | ×  | L   | н | н | н | н | н       | L  | L  | L  | н  |  |  |

| L  | × | X | L  | н   | н | н | н | н | н       | L  | н  | L  | н  |  |  |

| L  | × | L | н  | н   | н | н | н | н | H       | H  | L  | L  | н  |  |  |

| L  | L | н | н  | н   | н | н | н | н | H       | н  | н  | L  | н  |  |  |

Si en esta tabla se cambia como se mira la polaridad de las salidas A2, A1 y A0, que pasan a estar en lógica positiva, entonces en la tercera línea se genera la salida (A2 A1 A0) =  $(000)_2$ , por lo que la línea que fija el valor de las salidas tiene que ser I0. Esto se mantiene en todas las filas de la tabla: si se fijan las salidas  $(001)_2$  la entrada prioritaria es I1. Esto significa que las entradas están en prioridad baja conectándolas en orden inverso.; la entrada 7 es I0, la 6 es I1, la 5 es I2, ..., la 1 es I6 y la 0 es I7. La tabla lógica del circuito 74'148 sería esta:

| E1 | <b>I7</b> | <b>I6</b> | <b>I5</b> | <b>I</b> 4 | <b>I3</b> | I2 | I1 | 10 | A2 | A1 | A0 | GS | E0 |

|----|-----------|-----------|-----------|------------|-----------|----|----|----|----|----|----|----|----|

| 0  | X         | X         | X         | X          | X         | X  | X  | X  | 1  | 1  | 1  | 0  | 0  |

| 1  | 0         | 0         | 0         | 0          | 0         | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 1  |

| 1  | X         | X         | X         | X          | X         | X  | X  | 1  | 0  | 0  | 0  | 1  | 0  |

| 1  | X         | X         | X         | X          | X         | X  | 1  | 0  | 0  | 0  | 1  | 1  | 0  |

| 1  | X         | X         | X         | X          | X         | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 0  |

| 1  | X         | X         | X         | X          | 1         | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  |

| 1  | X         | X         | X         | 1          | 0         | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 0  |

| 1  | X         | X         | 1         | 0          | 0         | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 0  |

| 1  | X         | 1         | 0         | 0          | 0         | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  |

| 1  | 1         | 0         | 0         | 0          | 0         | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  |

| 1  | 0         | 0         | 0         | 0          | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

El circuito resultante es este. No hay que tener en cuenta las burbujas de inversión del esquemático, solo la definición .H o .L de las líneas.

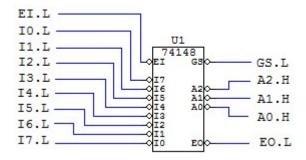

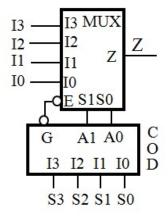

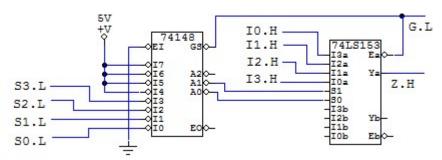

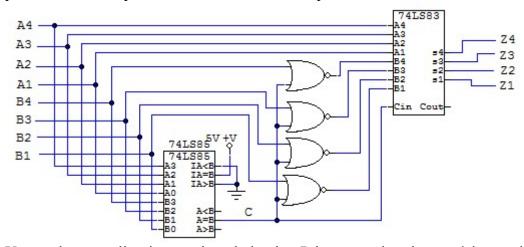

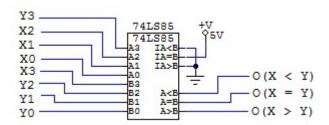

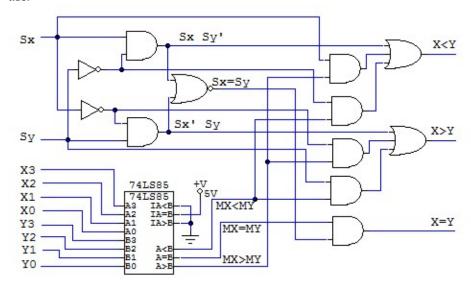

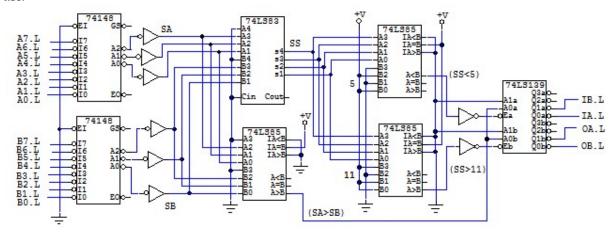

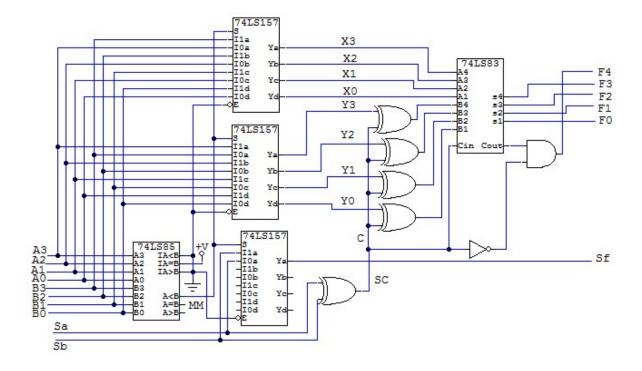

Página 7\_1. Diseñar un circuito multiplexor con prioridad de 4 bits. El circuito tiene 4 entradas de datos (I3-I0), 4 entradas de selección (S3-S0) y dos salidas Z y G. Cuando una o más de las entradas S están a 1, Z toma el valor de la entrada Ii, siendo i es el índice más alto de las entradas Si que están a 1; si todas las entradas S3-S0 están a 0, entonces Z toma el valor 0. La salida G se fija a 1 si al menos alguna entrada Si está a 1, en caso contrario se fija a 0. Utilizar en el diseño circuitos MSI convencionales: un 74LS148 (8 a 3 HPRI COD) y un circuito 74LS153 (4-input MUX).

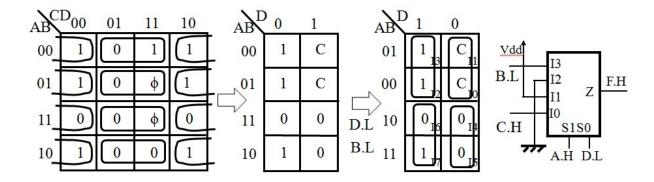

El enunciado es el mismo que el de la página 1. La tabla de ese problema se puede modificar de forma que defina un sistema basado en un codificador con prioridad y un multiplexor, tal que el codificador con prioridad lee las entradas S y genera el índice en binario, del S más alto a 1 en dos salidas A1A0. A1 y A0 son las entradas de un multiplexor convencional de cuatro entradas que pasan la entrada I a la salida Z.

| S3 | S2 | S1 | S0 | A1 | A0 | Z  | G |

|----|----|----|----|----|----|----|---|

| 1  | X  | X  | X  | 1  | 1  | I3 | 1 |

| 0  | 1  | X  | X  | 1  | 0  | I2 | 1 |

| 0  | 0  | 1  | X  | 0  | 1  | I1 | 1 |

| 0  | 0  | 0  | 1  | 0  | 0  | 10 | 1 |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 |

La implementación inicial necesita un codificador con prioridad alta 4 a 2 de entradas S3-S0 conectadas a sus entradas I3-I0; las salidas del codificador (A1A0) se conectan a las entradas de selección (S1S0) de un multiplexor de 4 entradas (I3-I0), y la salida G del codificador a la entrada de habilitación, para dejar la salida del multiplexor a 0 cuando no hay ninguna entrada S a 1.

La implementación se hace con circuitos de la familia 74: codificador con prioridad alta 8 a 3 74LS148 (diapositiva 34 de teoría) y multiplexor de cuatro entradas 74LS153 (diapositiva 5 de teoría). Como el codificador es 8 a 3, le convierto en 4 a 2 fijando las entradas 7-4 a 0, que es tensión alta H, ya que las entradas están en lógica negativa. Igualmente, las entradas S3-S0, tienen que definirse en lógica negativa. El circuito 74'153 tiene dos multiplexores de 4 entradas, de los que solo necesito uno. La salida GS del codificador se conecta a la entrada de habilitación del multiplexor: si todas las entradas del codificador están a 0 (H), GS está a 0 (H), el *enable* del multiplexor está a 0 (H), el multiplexor se deshabilita y su salida se fija a 0 (L). Al conectar las salidas del codificador (.L) a las entradas de selección del multiplexor (.H) hay un problema, ya que la polaridad de las señales es distinta. La solución directa para solventar este problema es usar inversores como en la figura.

Pero existe otra solución mejor, que evita los inversores, realizando las conexiones entre (A1A0) y (S1S0) directamente. Basta con modificar donde se colocan las entradas de datos del multiplexor. Por ejemplo, si la entrada S3 es 1 (L, Z = I3), el codificador fija A1A0 a 11 (LL), y las entradas del multiplexor (S1S0) leen 00 (LL), con lo que su entrada I0 pasa a Z; entonces la entrada I3 del multiplexor con prioridad debe situarse en la entrada I0 del multiplexor. Lo mismo puede comprobarse con el resto de valores en las entradas S3, S2, S1 y S0. El circuito queda:

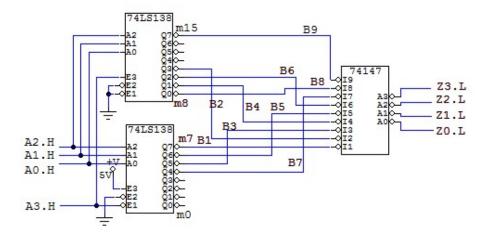

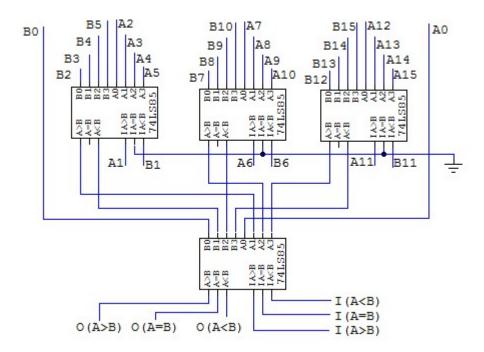

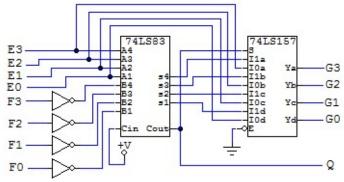

Página 7\_2. Realizar un circuito conversor del código BCD con pesos (8, 7, -2, -4) al código NBCD (8, 4, 2, 1) usando únicamente circuitos 74'138 (decodificador 3 a 8) y 74'147 (codificador con prioridad alta 10 a 4).

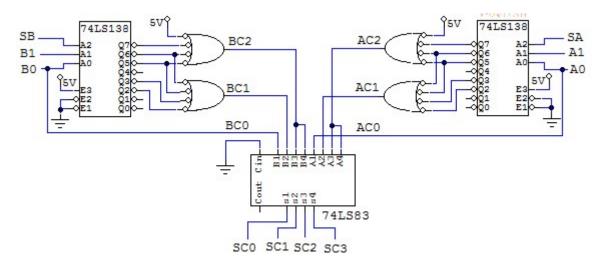

El circuito tiene una entrada A de 4 bits (A3 A2 A1 A0) que codifica el código BCD de entrada con pesos (8, 7, -2, -4), que ya ha aparecido en problema de otros temas, y una salida Z de cuatro bits (Z3 Z2 Z1 Z0) que codifica el código NBCD. Este problema se podría resolver con mapas de Karnaugh, pero se va a realizar con los circuitos indicados en el enunciado. Los circuitos 74'138 y 74'147 aparecen en las diapositivas 14 y 31 de teoría, respectivamente. El método para generar el circuito es usar un sistema decodificador/codificador. El decodificador convierte A en un valor intermedio B de 10 bits, y el codificador codifica los 10 bits de B en cuatro bits de Z.

|   | 8         | 7         | -2 | -4        | İ  |           |    |           |           |           |           |           |           |           |           | 8         | 4         | 2  | 1  |

|---|-----------|-----------|----|-----------|----|-----------|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----|----|

| D | <b>A3</b> | <b>A2</b> | A1 | <b>A0</b> | 0  | <b>B9</b> | B8 | <b>B7</b> | <b>B6</b> | <b>B5</b> | <b>B4</b> | <b>B3</b> | <b>B2</b> | <b>B1</b> | <b>B0</b> | <b>A3</b> | <b>A2</b> | A1 | A0 |

| 0 | 0         | 0         | 0  | 0         | 0  | 0         | 0  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 0         | 0         | 0  | 0  |

| 1 | 0         | 1         | 1  | 1         | 7  | 0         | 0  | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 0         | 0         | 0         | 0  | 1  |

| 2 | 1         | 0         | 1  | 1         | 11 | 0         | 0  | 0         | 0         | 0         | 0         | 0         | 1         | 0         | 0         | 0         | 0         | 1  | 0  |

| 3 | 0         | 1         | 0  | 1         | 5  | 0         | 0  | 0         | 0         | 0         | 0         | 1         | 0         | 0         | 0         | 0         | 0         | 1  | 1  |

| 4 | 1         | 0         | 0  | 1         | 9  | 0         | 0  | 0         | 0         | 0         | 1         | 0         | 0         | 0         | 0         | 0         | 1         | 0  | 0  |

| 5 | 0         | 1         | 1  | 0         | 6  | 0         | 0  | 0         | 0         | 1         | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 0  | 1  |

| 6 | 1         | 0         | 1  | 0         | 10 | 0         | 0  | 0         | 1         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 1  | 0  |

| 7 | 0         | 1         | 0  | 0         | 4  | 0         | 0  | 1         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 1  | 1  |

| 8 | 1         | 0         | 0  | 0         | 8  | 0         | 1  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 0         | 0  | 0  |

| 9 | 1         | 1         | 1  | 1         | 15 | 1         | 0  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 0         | 0  | 1  |

Con los circuitos 74'138 se puede formar un decodificador 4 a 16, seleccionando solamente 10 salidas. Cada combinación del código fija a 1 una salida del decodificador, que es uno de los bits B intermedios. Por ejemplo, el dígito 1 se codifica en A por 0111, que activa la salida m7 del decodificador y corresponde a la señal B1; el dígito 6 se codifica en A por 1010, que activa la salida m10 del decodificador y la señal B6. Las entradas A están en lógica positiva.

El convertidor 74'147 genera las salidas directamente en código NBCD. El circuito es un codificador con prioridad, aunque en este caso no es necesaria, ya que solo hay una entrada B a 1 cada vez. Se podría haber hecho con un codificador sin prioridad, hecho con puertas OR. Cada Bi se aplica a la entrada Ii del codificador, con i entre 1 y 9, lo que genera en Z el dígito D en NBCD. Si ninguna de las entradas B9–B1 están a 1, significa que B0 está a 1 y la salida es 0000 (dígito 0, NBCD). Las salidas Z están en lógica negativa. Para pasarlo a lógica positiva habría que usar inversores. El circuito queda así:

Página 7\_3. Se quiere realizar un circuito de 8 entradas (I7-I0) y 8 salidas (O7-O0), tal que la salida muestra la entrada, pero eliminando todos los unos menos el más significativo. Por ejemplo, si I="01101101", O="01000000"; si I="0001010", O="00010000"; etc. Si todos los bits de la entrada son 0, los de la salida también: I="00000000", O="00000000".

- a) Realizar un código VHDL para la descripción del problema.

- b) Implementar el circuito con un circuito codificador 8 a 3 74LS148 y un circuito decodificador 3 a 8 74LS138. Suponer las entradas y salidas I7.L, ... I0.L; O7.L, ... O0.L en polaridad negativa.

a) El código VHDL es similar al del problema 1. Se basa en una sentencia del tipo *if-elsif-else*, mirando los bits del más significativo al menos significativo, y cargando los valores de la salida bajo cada condición. Se puede hacer también una descripción genérica basada en un lazo *for*: se inicializan todos los bits de la salida a O a 0 con *others*, y cuando, en un lazo descendente, se encuentra el primer bit i de la entrada a 1, el bit i de la salida se fija a 1 y se abandona el lazo con la sentencia *exit*, por lo que el resto de los bits quedan a 0.

```

library ieee;

use ieee.std_logic_1164.all;

entity problema7 3 is

port (I: in std_logic_vector(7 downto 0);

O: out std logic vector(7 downto 0));

end problema7 3;

architecture uno of problema7 3 is

begin

process(I)

begin

if ( I(7) = '1') then 0 <= "10000000";

elsif ( I(6) = '1') then 0 <= "01000000";

elsif ( I(5) = '1') then 0 <= "00100000";

elsif ( I(4) = '1') then 0 <= "00010000";

elsif ( I(3) = '1') then 0 <= "00001000";

elsif ( I(2) = '1') then 0 <= "00000100";

elsif ( I(1) = '1') then O <= "00000010";

elsif ( I(0) = '1') then 0 <= "00000001";

else 0 <= "000000000";

end if;

end process;

end uno:

```

```

library ieee;

use ieee.std logic 1164.all;

entity problema7 3gen is

generic(N: integer := 8);

port (I: in std logic vector (N-1 downto 0);

O: out std_logic_vector(N-1 downto 0));

end problema7_3gen;

architecture uno of problema7 3gen is

process(I)

begin

0 <= (others => '0');

for j in N-1 downto 0 loop

if (I(j) = '1') then

O(j) <= '1';

exit:

end if;

end loop;

end process;

end uno:

```

**b)** El funcionamiento del circuito para 8 bits puede verse en una tabla de entradas y salidas, donde defino unas señales intermedias A de tres bits A2, A1 y A0, que codifican en binario el índice más alto de las entradas fijadas a 1.

| I | Ι | I | I | I | I | Ι | I | A | A | A | О | О | О | О | О | О | О | О |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 2 | 1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | X | X | X | X | X | X | X | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | X | X | X | X | X | X | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | X | X | X | X | X | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | X | X | X | X | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 1 | X | X | X | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 | X | X | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

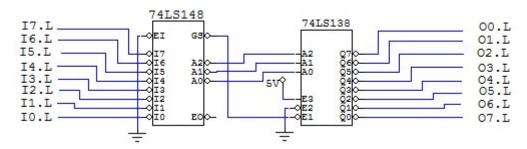

Al estudiar las señales se puede ver que las señales A son la respuesta de un codificador con prioridad alta de 8 a 3. A su vez las salidas O son la respuesta de un decodificador de 3 a 8 con entradas A. Para conseguir que cuando todas las entradas I estén a 0 se puede usar la salida GS de un codificador y conectarlo a la entrada de habilitación del decodificador. Ahora ya se puede construir el circuito con el codificador 74LS148 (diapositiva 34 de teoría) y el decodificador 74LS138 (diapositiva 14 de teoría). El problema al conectar los circuitos es que las salidas del codificador están en lógica negativa, mientras que las entradas de los decodificadores están en lógica positiva. Al igual que en el problema 7\_1 hay dos formas de ajustar el circuito, la primera

consiste en situar inversores entre las salidas del codificador y las entradas del decodificador. La segunda consiste en "mover" la posición de las salidas: si el codificador genere el índice 7 (111) en lógica negativa es voltaje bajo (LLL); el decodificador lee (LLL) pero en lógica positiva eso es (000), luego fija a 1 la salida O0. Esto implica que en la salida O0 del codificador está realmente la salida O7 del problema. Si se hace con todas las salidas, complementando los bits de A, se pasa de  $0 \Leftrightarrow 7$ ,  $1 \Leftrightarrow 6$ ,  $2 \Leftrightarrow 5$  y  $3 \Leftrightarrow 4$ . Con todo esto el circuito, para entradas y salidas .L queda así:

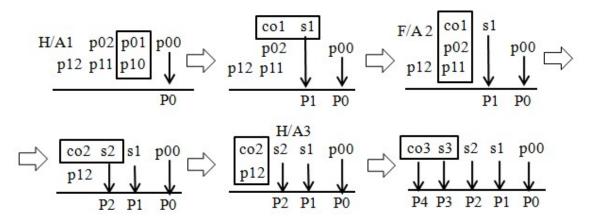

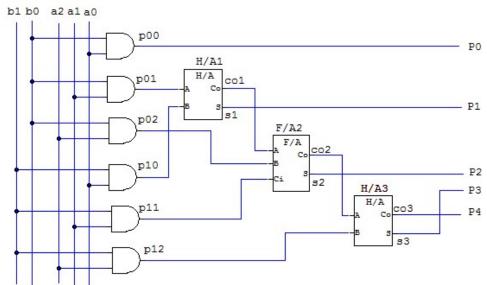

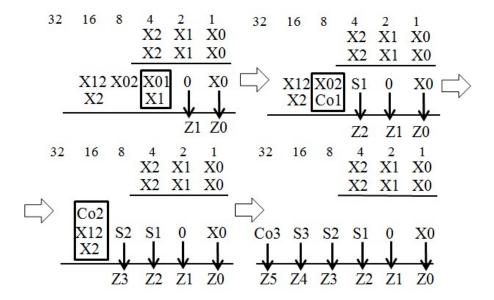

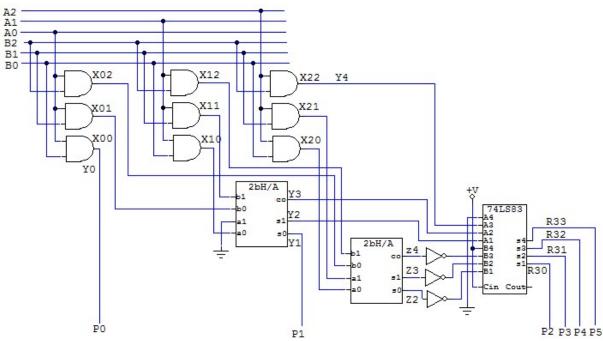

Página 8\_1. Diseñar utilizando únicamente semisumadores y sumadores completos un circuito digital que realice la multiplicación de un número binario de dos bits por otro de tres bits.

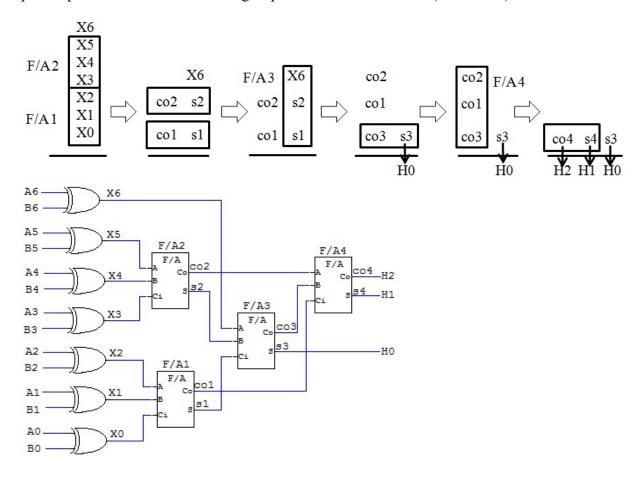

Se dispone de un multiplicando A de tres bits (a2 a1 a0, valores de 0 a 7) y un multiplicador B de dos bits (b1 b0, valores de 0 a 3). El resultado P debe ser de 5 bits (P4 P3 P2 P1 P0, valor máximo 7 \* 3 = 21). Planteo el algoritmo de suma basado en productos parciales aritméticos de 1 bit, pij = bi \* aj, que ya se sabe que puede hacerse con una puerta AND. En total hay 6 puertas AND. Y esos términos se suman con sumadores completos (F/A) o semisumadores (H/A) de 1 bit.

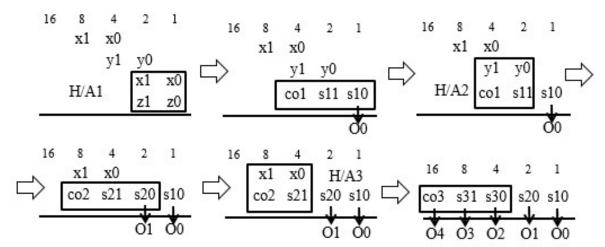

Para realizar la suma se pueden seguir estos pasos, donde se indican los sumadores completos y los semisumadores que se utilizan:

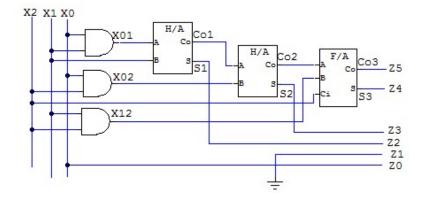

El circuito asociado, indicando las AND y los sumadores queda:

Página 8\_2. Diseñar un circuito que calcule la distancia de Hamming de dos palabras A y B de 7 bits usando el menor número posible de puertas lógicas y/o de dispositivos MSI.

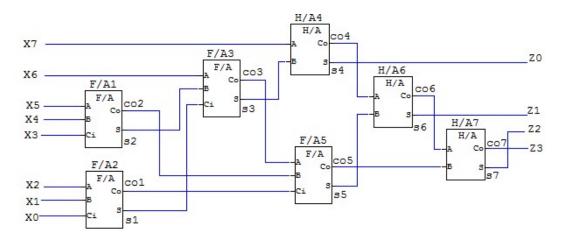

La distancia de Hamming de dos palabras de N bits es el número de posiciones en las que los valores de los bits son distintos. Por tanto, la distancia de Hamming puede tomar valores entre 0 (palabras iguales) y N (todos los bits distintos). En este problema N es 7 (A6-A0 y B6-B0), por lo que la distancia de Hamming se puede codificar en 3 bits (H2 H1 H0).

Para realizar el circuito puedo empezar por comprobar si para cada posición i los bits de Ai y Bi son distintos. Ya ha aparecido varias veces esta condición y que  $Xi = (Ai \neq Bi) = Ai \oplus Bi$ , por lo que el circuito necesita 7 puertas XOR. Para saber el número en binario de posiciones distintas hay que "contar" el número de 1s en las Xi, y la forma de contar es sumar todos los bits usando "full-adders" o "half-adders". Hay que intentar sumar primero de los bits menos significativos a los más significativos, obteniendo un único bit en cada posición que será el bit del resultado. La suma de 7 bits del mismo peso se puede hacer con 4 "full-adders", según el esquema de sumas y el circuito de la figura anterior.

Página 8\_3. Diseñar utilizando elementos MSIs (sumadores y decodificadores) un circuito que calcule el resultado de una votación de siete votos. Cada voto aparece codificado mediante dos bits I1I0, de forma que la abstención se representa por 00, 'Si' por 01, 'No' por 10 y los votos nulos aparecen como 11. El resultado de la votación debe darse indicando el número de votos de cada tipo. Realizar lo mismo para una votación de ocho votos.

Este problema es muy parecido al problema anterior. Hay siete votantes que tienen cuatro opciones de voto. Para cada votante  $V_i$  se usa un decodificador, que tiene como entradas las señales  $I1_iI0_i$  que genera en su salida O0 la señal  $A_i$ , (Abstención), en su salida O1 la señal  $S_i$  (Si), en su salida O2 la señal  $N_i$  (No), y en su salida O3 la señal  $X_i$  (Nulo).

El número de votos de cada tipo está entre 0 y 7, por lo que requiere tres bits de salida por tipo: Va (abstenciones, Va2 Va1 Va0), Vs (síes, Vs2 Vs1 Vs0), Vn (noes, Vn2 Vn1 Vn0) y Vx (nulos, Vx2 Vx1 Vx0). Para pasar de las siete Ai a las tres Va hay que usar el circuito de suma del problema anterior formado por 4 "full-adders". Para cada uno de los otros tipos de salida (S<sub>i</sub> a Vs, N<sub>i</sub> a Vn y X<sub>i</sub> a Vx) también se requiere otro circuito de suma de 7 bits. El circuito total necesita 7 decodificadores y 16 "full-adders" (cuatro circuitos de suma de 7 bits).

Si la votación fuese de 8 votantes, el esquema es similar al de 7 votantes, pero el valor de las salidas debe estar entre 0 y 8, por lo que la salida Z necesita cuatro bits (Z3 Z2 Z1 Z0) por tipo de voto, y el circuito de suma es algo más complicado. El esquema anterior y el siguiente circuito corresponden al diseño de un sumador de 8 bits (X7-X0) con "full-adders" o "half-adders".

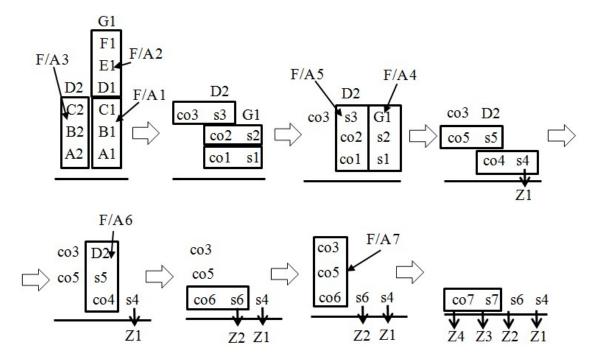

Página 8\_4. Realizar la suma de cuatro números de dos bits A (a2a1), B (b2b1), C (c2c1) y D (d2d1) y tres números de 1 bit, E (e1), F (f1) y G (g1) utilizando el menor número posible de sumadores completos ("full-adders").

El problema tiene 11 entradas, según indica y el resultado. Como el valor máximo A, B, C y D es 3 al ser de 2 bits, y el de E, F y G es 1 al ser de 1 bit, el resultado máximo de la suma es 15 (3+3+3+3+1+1+1), por ello la salida Z tiene 4 bits Z4, Z3, Z2 y Z1.

Como en problemas anteriores voy a sumar de tres en tres usando únicamente "full-adders" hasta conseguir que solo haya un bit por posición:

El circuito asociado a este esquema de sumas queda así:

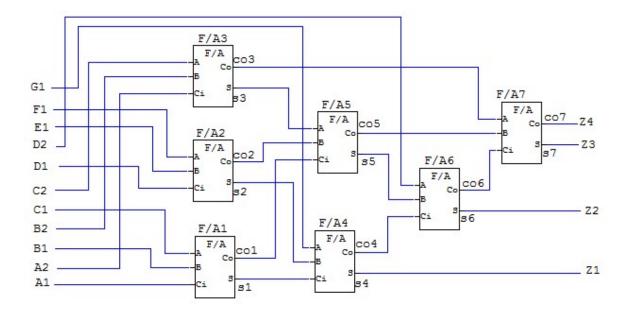

Página 9\_1. Diseñar un circuito que realice la operación aritmética: O = 5 X + 2 Y + Z

para operandos X (x1x0), Y (y1y0) y Z (z1z0) de dos bits, utilizando el menor número posible de semisumadores de dos bits de operandos de entradas A (a1a0) y B (b1b0).

Este problema se resuelve haciendo sumas. Tenemos 6 entradas en X, Y y Z con valores entre 0 y 3; para saber el número de salidas, obtengo el resultado máximo O = 5\*3+2\*3+3 = 24, y para codificar 24 en binario necesito cinco bits (O4 O3 O2 O1 O0). El sumador que se debe usar es un "half-adder" de dos bits, que suma las entradas de dos bits A, B sin acarreo de entrada, y genera un resultado de tres bits dos de suma y el acarreo de salida: (a1a0) PLUS (b1b0) = (Co S1 S0).

Para sumar los operados un método incorrecto sería sumar 5 veces X, 2 veces Y y una vez Z, ya que el circuito sería muy grande. Para reducir el circuito hay que darse cuenta que si multiplico un dato por una potencia de 2, basta desplazar el dato a la izquierda tantas posiciones como la potencia de 2, al igual que hacemos con las potencias de 10 cuando usamos aritmética decimal. Así:

$$O = 5 X + 2 Y + Z = 4 X + X + 2 Y + Z = 2^{2} X + X + 2^{1} Y + Z = (X00) + X + (Y0) + Z$$

Agrupo los bits para sumar con el menor número de "half-adders". Para reducir el circuito hay que sumar los bits menos significativos primero, hasta conseguir un único bit por peso de derecha a izquierda, lo que evita tener que propagar acarreos; los bits únicos en las columnas de la derecha son los bits de la solución. La solución sigue estos pasos:

Del esquema se obtiene el circuito:

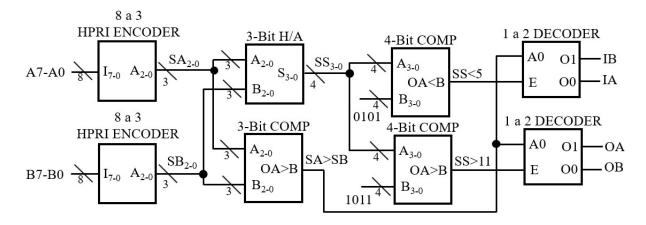

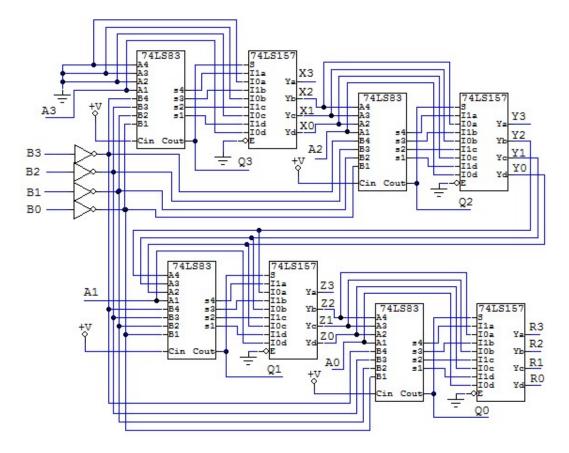

Página 9\_2. Un sistema digital accede a los elementos de una matriz de 12\*12 (144 elementos) que están almacenados en memoria. Para acceder a un elemento de la matriz el sistema utiliza la posición de filas F y la posición de columnas C, ambas de 4 bits (F3-F0, C3-C0) en código binario con valores entre 0 y 11. Sin embargo, la memoria utilizada solo tiene un bus de direcciones D.

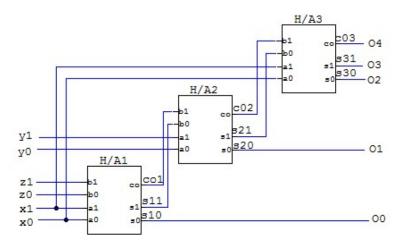

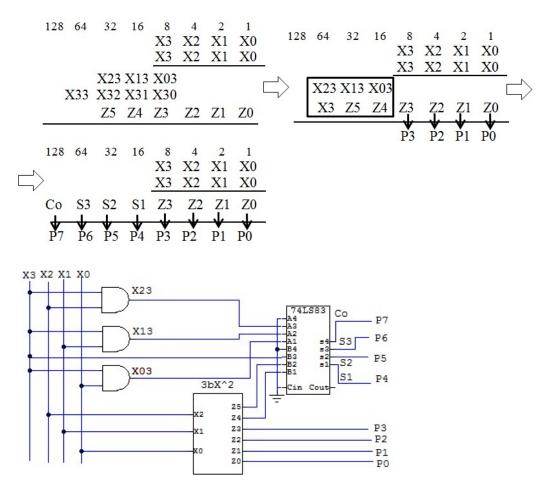

Diseñar un circuito que genere la dirección D (8 bits D7-D0, valores entre 0 y 143) del elemento de la matriz en memoria de la forma  $D = 12 \cdot F + C$ . Utilizar el menor número posible de sumadores (preferentemente 74LS83) para realizar la implementación.

Como se indica en el enunciado la salida es dirección D de 8 bits que toma valores entre 0 y 143 en binario, y las entradas son F y C, con valores entre 0 y 11, codificados en 4 bits en binario. Se calcula mediante la operación aritmética D = 12 F + C, que debe resolverse usando preferentemente sumadores "full-adders" de 4 bits 74LS83, cuya descripción está en la diapositiva 46 de teoría.

Para realizar la operación no se suma F doce veces, sino que se puede plantear unas multiplicaciones por potencias de 2, ya que multiplicar por una potencia N de 2 significa desplazar a la izquierda N bits. Así:

$$D = 12 F + C = 8 F + 4 F + C = 2^3 F + 2^2 F + C = (F000) + (F00) + C.$$

Hago un esquema de los bits a sumar y añado el esquema de la suma "full-adder" de 4 bits. Con estos elementos se puede realizar el problema usando dos sumadores. Relleno con 0s los huecos que quedan en los operandos de los sumadores, y los conecto a GND. Muestro un esquema posible de las sumas y del circuito correspondiente.

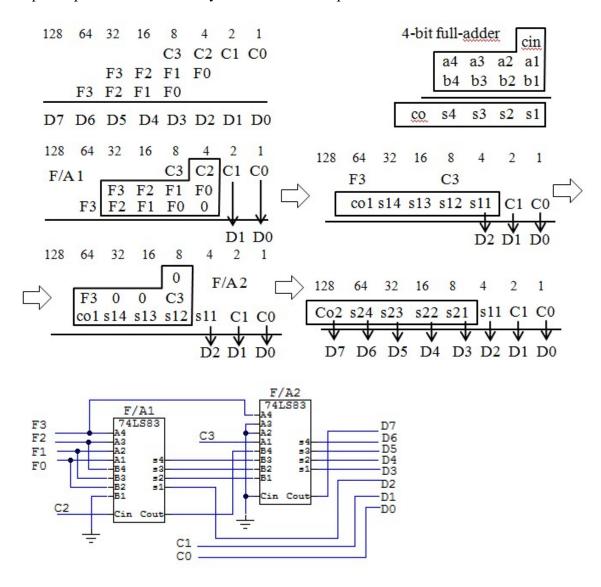

Página 9\_3. Realizar el diseño de un circuito que sume dos dígitos NBCD, dando el resultado en código NBCD, utilizando puertas lógicas cuando sea necesario. Indicar como puede utilizarse este circuito para sumar números NBCD de más de un dígito. Ayuda: Hay que sumar 6.

Este problema se ha usado en un apartado de la práctica 2. Se supone que tenemos dos dígitos NBCD A (A4 A3 A2 A1) y B (B4 B3 B2 B1) de cuatro bits, y se quiere que el resultado de la suma aritmética A PLUS B también se muestre en código NBCD. Para resolver este problema hay que considerar que el resultado de la suma está entre 0 (0+0) y 18 (9+9), y que se codifica en dos dígitos NBCD D2 y D1. D1 puede tomar valores entre 0 y 9, por lo que requiere cuatro bits, mientras que D2 solo toma valores 0 o 1, por lo que solo necesita 1 bit.

El método de realizar la suma genera primero S = A PLUS B, donde S es el resultado de la suma en 5 bits (Co S4 S2 S3 S1). Hay que obtener una señal Z que indique si  $S \ge 10$  (Z es 1) o si S < 10 (Z es 0). Si S < 10 el resultado es correcto  $\Rightarrow D2 = Z = 0$ ; D1 = (S4 S3 S2 S1); pero

si  $S \ge 10$  se sabe que para D2 = Z = 1, pero para D1 hay que realizar otra suma para obtener Sx = S PLUS 6, si S es 10 (01010), entonces Sx es 16 (10000) que se puede dividir en BCD D2 D1 = 10 (D2 = Z = 1, D1 = 0000); si S es 18, entonces Sx es 24 (11000), que se divide en NBCD D2D1 = 18 (D2 = Z = 1, D1 = 1000).

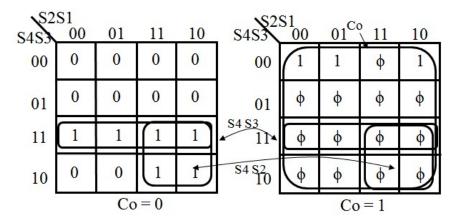

Este método requiere tres subcircuitos. Primero, un sumador para hacer A PLUS B: un sumador como el 74LS83 con el bit de acarreo a 0. Segundo, un circuito que genere la señal Z ( $S \ge 10$ ); la función lógica de Z la calculo mediante un mapa de Karnaugh sabiendo que S está entre 0 y 18 (para el resto de valores puedo considerar Z como "don't care"). Z = Co + S4 S3 + S4 S2. Z también podría generarse con un circuito comparador.

El tercer circuito es un sumador que sume 6 si Z es 0 y 0 si Z es 1. El sumador extra puede hacerse como S PLUS (0 Z Z 0), fijando el bit de acarreo a 0. El sumador podría ser solo de 3 bits ya que el bit menos significativo de D1 es directamente S1. El circuito queda como en la figura. El bit de D2 también puede obtenerse del acarreo de salida del segundo sumador.

Para sumar números de varios dígitos BCD, el circuito de la figura puede considerarse como un semisumador (sin acarreo de entrada), siendo D1 el dígito de suma y D2 el acarreo de salida. Si en el circuito en el sumador de la izquierda se considera que en el acarreo de entrada Cin se puede conectar una entrada de un bit, que actué como acarreo de entrada del sumador BCD se tendría un sumador completo BCD. La suma de un sumador completo BCD estaría entre 0 y 19, pero esto no alteraría el cálculo de Z ya que, si la casilla 19 del mapa de Karnaugh anterior se cambia de  $\phi$  a 1, su función lógica no cambia. Se puede generar una estructura de suma tipo *ripple*, conectando el acarreo de salida (D2) generado por dígito i al acarreo de entrada de la suma del siguiente dígito i+1.

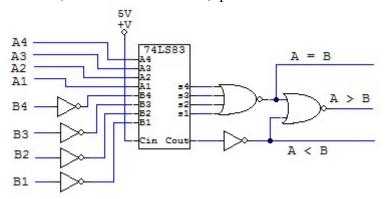

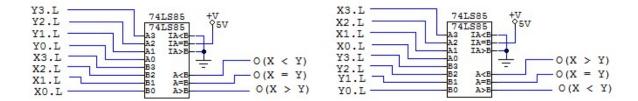

Página  $10_{-}1$ . Realizar el diseño de un comparador de dos números A y B de cuatro bits tomando como base el sumador de números binarios de cuatro bits 74'83, utilizando puertas lógicas cuando sea necesario. El circuito debe generar tres salidas: O1 (A = B), O2 (A > B), O3 (A < B).

La base de este circuito consiste en hacer una resta. Si hago A - B y el resultado es 0, entonces A = B; si es positivo es que A > B, y si es negativo es que A < B. La resta en circuitos digitales se hace operando en complemento-2, y el circuito restador se muestra en la diapositiva 47 de teoría. En ese circuito se utiliza  $A - B = A + (B)_{2,c} = A + \overline{B} + 1$ .

El complemento-2 también se puede definir de otra manera  $A - B = A + (2^N - B)$  (diapositiva 21 del tema I). Si uso la expresión  $A - B = 2^N + (A - B)$ , donde  $2^N$  es el peso de la salida de acarreo del sumador operando como restador. De esta expresión se pueden obtener las salidas de un comparador:

- Si A < B =>

$$2^{N}$$

+ (A - B) <  $2^{N}$  => Cout = 0; S  $\neq$  0

- Si A = B =>  $2^{N}$  + (A - B) =  $2^{N}$  => Cout = 1; S = 0

- Si A > B =>  $2^{N}$  + (A - B) >  $2^{N}$  => Cout = 1; S  $\neq$  0

Comparando con los valores de Cout y de S:

```

- A < B si Cout es 0 => (A < B) = \overline{\text{Cout}}

- A = B si S es 0 => (A = B) = \overline{\text{S4}} \overline{\text{S3}} \overline{\text{S2}} \overline{\text{S1}} = \overline{\text{S4}} + \overline{\text{S3}} + \overline{\text{S2}} + \overline{\text{S1}}

- A > B si Cout = 1 y S \neq 0 => (A > B) = Cout (S4 + S3 + S2 + S1) = Cout \bullet \overline{\text{(A = B)}} = \overline{\text{Cout}} + (A = B)

```

El circuito, basado en un restador, queda así:

Página  $10_2$ . Diseñar un circuito que realice la operación aritmética Z = A + 1 cuando A es igual B, y la operación aritmética Z = (A - B) - 1 cuando A es mayor que B, donde A y B son números binarios de cuatro bits, siendo siempre A mayor o igual que B. Implementar el circuito utilizando como base el sumador 74'83 y otros elementos MSI y puertas lógicas.

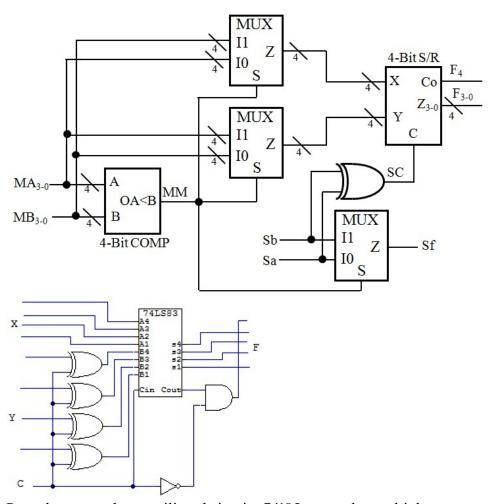

Según el enunciado hay varias operaciones que se deben realizar. Por un lado, hay que comparar A y B para ver si A > B o A = B (A > B) no está permitido. Este comparador genera una señal de control C para realizar una de las operaciones aritméticas. La operación aritmética "A + 1", se puede realizar con un sumador. La operación "A - B - 1", se puede realizar como una suma en complemento-2, haciendo la transformación "A + ( $\overline{B}$  + 1) - 1", o "A +  $\overline{B}$ ". Las operaciones por realizar se pueden plantear en una tabla, donde indico los valores que tienen

que tomar cada operando del sumador 74'83 de 4 bits: Asum (4 bits), Bsum (4 bits), Cin (1 bit).

|       | C | Op.   | Asum | Bsum                    | Cin |

|-------|---|-------|------|-------------------------|-----|

| A > B | 0 | A-B-1 | A    | $\overline{\mathrm{B}}$ | 0   |

| A = B | 1 | A + 1 | A    | 0                       | 1   |

De esta tabla se obtiene que C es la salida "igual" de un comparador de 4 bits (74'85 por ejemplo), y que Asum = A y Cin = C. Para calcular Bsum utilizo, como si fuese un multiplexor seleccionado por C, la expresión Bsum =  $\overline{C} \overline{B} + C \bullet 0 = \overline{C} \overline{B} = \overline{C + B}$ , que son en realidad 4 puertas NOR, una por cada bit de B. El circuito queda: