# Codificadores con prioridad

## **Definición**

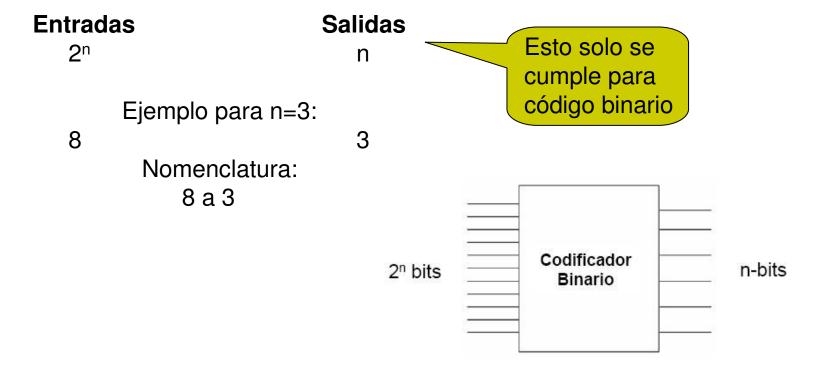

Un **codificador** es un circuito combinacional con 2<sup>n</sup> entradas y n salidas, cuya función es presentar en la salida el código binario correspondiente al índice de la entrada activada.

El rango de entradas válido corresponde a las salidas típicas de un decodificador (sólo una entrada a 1). Otras combinaciones (más de una entrada a 1) producirían error en la salida.

| $I_7$ | $I_6$ | $I_5$ | $L_4$ | $I_3$ | $I_2$ | $I_1$ | $I_0$ | O <sub>2</sub> | 01 | O <sub>0</sub> |

|-------|-------|-------|-------|-------|-------|-------|-------|----------------|----|----------------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0              | 0  | 0              |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0              | 0  | 1              |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0              | 1  | 0              |

| 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0              | 1  | 1              |

| 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1              | 0  | 0              |

| 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 1              | 0  | 1              |

| 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1              | 1  | 0              |

| 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1              | 1  | 1              |

$$O2 = 14 + 15 + 16 + 17$$

$O1 = 12 + 13 + 16 + 17$

$O0 = 11 + 13 + 15 + 17$

Este tipo de codificadores es usado únicamente cuando el rango de datos de entrada está correctamente acotado y su funcionamiento garantizado.

No se comercializa con ellos ya que su funcionamiento se basa únicamente en puertas OR

En estos circuitos, cuando existe más de una señal activa, la salida codifica típicamente la de mayor prioridad (HPRI, corresponde al bit de mayor índice), ó la de menor prioridad (LPRI, corresponde al bit de menor índice), .

| $I_7$ | $I_6$ | $I_5$ | $\mathbf{L}_{4}$ | $I_3$ | $I_2$ | $I_1$ | $I_0$ | 02 | $O_1$ | O <sub>0</sub> |

|-------|-------|-------|------------------|-------|-------|-------|-------|----|-------|----------------|

| 0     | 0     | 0     | 0                | 0     | 0     | 0     | 1     | 0  | 0     | 0              |

| 0     | 0     | 0     | 0                | 0     | 0     | 1     | X     | 0  | 0     | 1              |

| 0     | 0     | 0     | 0                | 0     | 1     | X     | X     | 0  | 1     | 0              |

| 0     | 0     | 0     | 0                | 1     | Х     | X     | X     | 0  | 1     | 1              |

| 0     | 0     | 0     | 1                | X     | X     | X     | X     | 1  | 0     | 0              |

| 0     | 0     | 1     | X                | X     | X     | X     | X     | 1  | 0     | 1              |

| 0     | 1     | X     | Х                | X     | X     | Х     | Х     | 1  | 1     | 0              |

| 1     | X     | X     | X                | X     | X     | X     | X     | 1  | 1     | 1              |

**HPRI**

Tabla:

| l <sub>3</sub> | l <sub>2</sub> | I <sub>1</sub> | I <sub>0</sub> | O <sub>1</sub> | O <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              | 0              | 0              | 1              | 0              | 0              |

| 0              | 0              | 1              | Х              | 0              | 1              |

| 0              | 1              | Х              | Х              | 1              | 0              |

| 1              | Х              | X              | Х              | 1              | 1              |

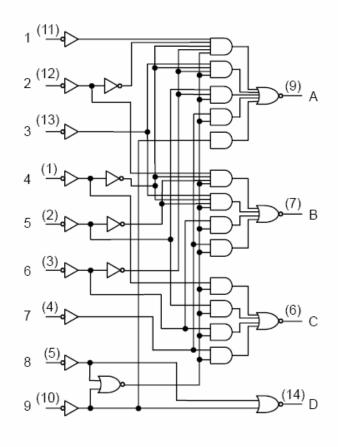

O1=

$$12^{+}\overline{\cancel{13}} + 13 = 12 + 13$$

O0= $\overline{\cancel{13}}^{+}\overline{\cancel{12}}^{+}11+13=13+\overline{\cancel{12}}^{+}11$

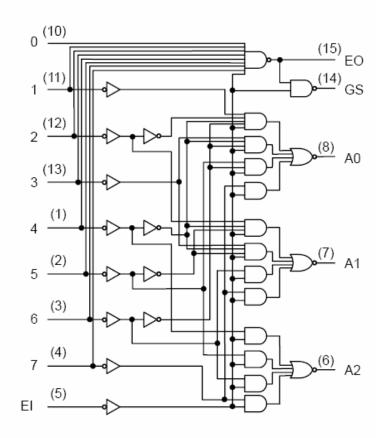

Esquema de este codificador por dentro:

## Descripción VHDL

```

Library ieee:

Use.ieee.std logic 1164.all

Entity cod is

Port

(I: in std_logic_vector(3 downto 0); -- Entradas

A: out std_logic_vector(1 downto 0); -- Salidas

Z: in std logic);

-- Indica alguna entrada a 1

End cod:

Architecture comportamiento of cod is

Begin

Process (I,Z)

Begin

If (I(3)='1') then

A<="11";

Codificador 4 a 2

elsif (I(2)='1') then

A<="10";

elsif (I(1)='1') then

A<="01":

Else A<="00":

End if:

If (I = "0000") then Z <= '0'

else Z <= '1':

end if:

End process;

End comportamiento;

```

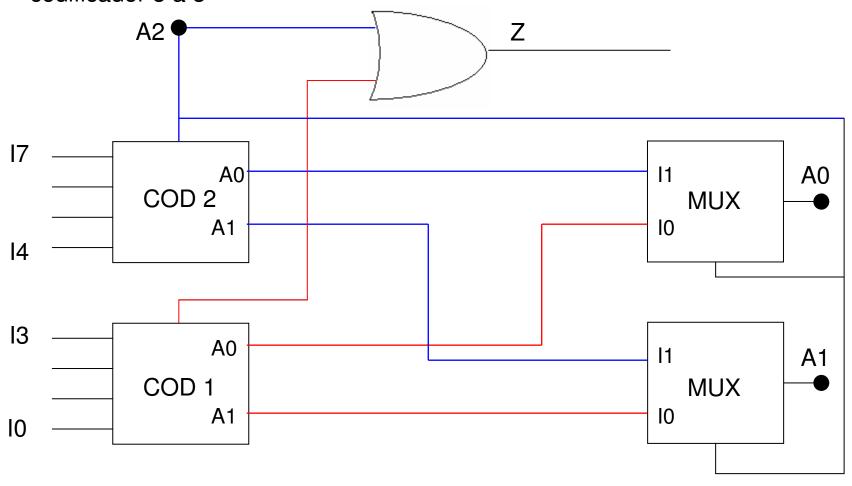

Con dos codificadores 4 a 2 y dos multiplexores podemos fabricar un codificador 8 a 3

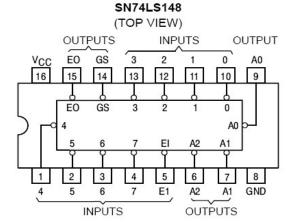

### Familia 74

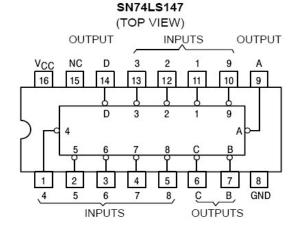

SN74LS147, SN74LS148

#### SN74LS147 FUNCTION TABLE

|   | INPUTS |   |   |   |   |   |   |   |   |   | PUTS | 3 |

|---|--------|---|---|---|---|---|---|---|---|---|------|---|

| 1 | 2      | 3 | 4 | 5 | 6 | 7 | 8 | 9 | D | С | В    | Α |

| Н | Н      | Н | Н | Н | Н | Н | Н | Н | Н | Н | Н    | Н |

| X | X      | X | X | X | X | X | X | L | L | Н | Н    | L |

| X | X      | X | X | X | X | X | L | Н | L | Н | Н    | Н |

| X | X      | X | X | X | X | L | Н | Н | Н | L | L    | L |

| X | X      | X | X | X | L | Н | H | Н | Н | L | L    | Н |

| X | X      | X | X | L | Н | Н | Н | Н | Н | L | Н    | L |

| X | X      | X | L | Н | Н | Н | Н | Н | Н | L | Н    | Н |

| X | X      | L | Н | Н | Н | Н | Н | Н | Н | Н | L    | L |

| X | L      | Н | Н | Н | Н | Н | Н | Н | Н | Н | L    | Н |

| L | Н      | Н | Н | Н | Н | Н | Н | Н | Н | Н | Н    | L |

H = HIGH Logic Level, L = LOW Logic Level, X = Irrelevant

#### SN74LS148 FUNCTION TABLE

|    |   |   | IN | PUT | rs | OUTPUTS |   |   |    |    |    |    |    |

|----|---|---|----|-----|----|---------|---|---|----|----|----|----|----|

| EI | 0 | 1 | 2  | 3   | 4  | 5       | 6 | 7 | A2 | A1 | A0 | GS | EO |

| Н  | Х | Х | Х  | Х   | Х  | Х       | Х | Х | Н  | Н  | Н  | Н  | Н  |

| L  | Н | Н | Н  | Н   | Н  | Н       | Н | Н | Н  | H  | Н  | Н  | L  |

| L  | X | X | X  | X   | X  | X       | X | L | L  | L  | L  | L  | Н  |

| L  | X | X | X  | X   | X  | X       | L | Н | L  | L  | Н  | L  | Н  |

| L  | X | X | Χ  | X   | X  | L       | Н | Н | L  | Н  | L  | L  | Н  |

| L  | X | X | X  | X   | L  | Н       | Н | Н | L  | Н  | Н  | L  | Н  |

| L  | X | X | X  | L   | Н  | Н       | H | Н | Н  | L  | L  | L  | Н  |

| L  | Χ | X | L  | Н   | Н  | Н       | Н | Н | Н  | L  | Н  | L  | Н  |

| L  | Χ | L | Н  | Н   | Н  | Н       | Н | Н | Н  | Н  | L  | L  | Н  |

| L  | L | Н | Н  | Н   | Н  | Н       | Н | Н | Н  | Н  | Н  | L  | Н  |

## Familia 74

#### **FUNCTIONAL BLOCK DIAGRAMS**

SN74LS147

SN74LS148

# **Aplicación**

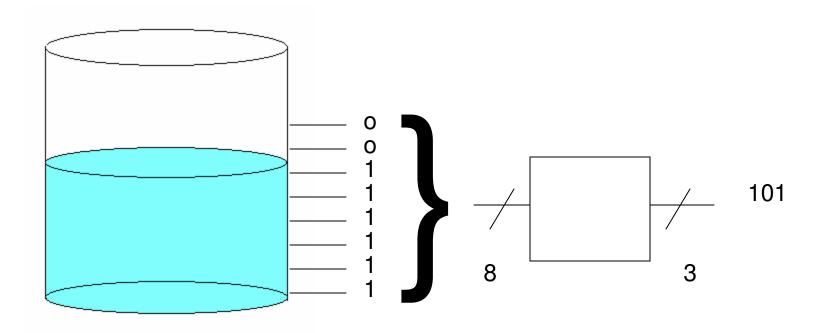

#### Bidón con 8 sensores

## **Ejercicios**

- 1.Calcular las salidas de un codificador de prioridad con 4 entradas (I0,I1,I2,I3)=(L,H,H,L):

- a) Prioridad alta y entradas en polaridad negativa

- b) Prioridad baja y entradas en polaridad negativa

- c) Prioridad baja y entradas en polaridad positiva

- 2.Obtener las ecuaciones lógicas minimizadas que permiten encontrar cuál de 7 líneas de entrada A1,A4,A6,A8,A9,A13,A14 está puesta a valor lógico 1,dando como resultado su correspondiente codificación binaria.

- a) Sólo una entrada está a 1 cada vez.

- b) Se permite que varias líneas de entrada estén simultáneamente a 1, en la salida se obtiene el índice más bajo de las entradas a 1.

- 3.Se quiere realizar un circuito de 8 entradas (I8-I1) y 8 salidas (O8-O1), tal que la salida muestra la entrada pero eliminando todos los unos menos el mas significativo. Por ejemplo si I="01101101", O="01000000". Si todos lo bits de entrada son 0, los de salida también.

- -Implementar el circuito con un codificador 8 a 3 y un decodificador 3 a 8.

- -Implementar el circuito con un codificador 74'148 (8 a 3) y un decodificador 74'138 (3 a 8). Suponer las entradas I y las salidas O asertadas bajas.